JTAGKey2Cloneをもっと使ってみる

20150514追:

2015年現在、JTAGKey2CompatibleのRev.5まで

上がっています。自作される場合はこちらを参考にしてください。

20150514追:

よし

やっと日記書く余裕ができた…MTM05に参加された皆様、本当にお疲れ様でした。

日記はぢめてもう1年たったことだし、ねむいさんもていどひくいと言われないような

仕事をしたいものです。本業の虹メの方がスレの途中で寝落ちしまくっててていどひくいどころ

じゃない状態なのは置いといて。てかいつもスレに参加してくれてる人ごめんなさい…。

さて本題、前回はJTAGkey2のクローンを作成し、LPC2388のフラッシュプ

ログラミングでRTCKの威力を確認しましたが、今回もう少し設定をなぶってみました。

CQ-FRK-NXP-ARMの基板は12MHzの外部クロックが乗っているのでOpenOCD接続時に

デフォルトの内部4MHzRC発振からそちらで動くように切り替えると速度が速くなる

わけですが、PLL使って最高速の72MHzまで叩き上げるとさらに速くなるはずです!

(もう十分早いけど)

↓というわけで試して比較してみました。

●Ext12MHz,With AdaptiveClocking(RTCK),CCLK=12MHz

> > "C:/Devz/AVR/WinAVR/utils/bin/make.exe" program

> openocd -f C:/Devz/ARM/OCD/daemon.cfg -f C:/Devz/ARM/OCD/tcl/interface/jtagkey2.cfg -f C:/Devz/ARM/OCD/tcl/target/lpc2388_rclk_flash.cfg -c "mt_flash main.elf"

> Open On-Chip Debugger 0.5.0-dev-00267-gef72484 (2010-05-26-21:28)

> Licensed under GNU GPL v2

> For bug reports, read

> http://openocd.berlios.de/doc/doxygen/bugs.html

> adapter_nsrst_delay: 100

> jtag_ntrst_delay: 100

> trst_and_srst srst_pulls_trst srst_gates_jtag trst_push_pull srst_open_drain

> RCLK - adaptive

> RCLK - adaptive

> fast memory access is enabled

> dcc downloads are enabled

> Info : device: 6 "2232H"

> Info : deviceID: 67358712

> Info : SerialNumber: 22222222A

> Info : Description: Amontec JTAGkey-2 A

> Info : max TCK change to: 30000 kHz

> Info : RCLK (adaptive clock speed)

> Info : JTAG tap: lpc2388.cpu tap/device found: 0x4f1f0f0f (mfg: 0x787, part: 0xf1f0, ver: 0x4)

> Info : Embedded ICE version 7

> Error: EmbeddedICE v7 handling might be broken

> Info : lpc2388.cpu: hardware has 2 breakpoint/watchpoint units

> target state: halted

> target halted in ARM state due to debug-request, current mode: User

> cpsr: 0x60000050 pc: 0x000038bc

> flash 'lpc2000' found at 0x00000000

> auto erase enabled

> wrote 131072 bytes from file main.elf in 2.671892s (47.906 KiB/s)

> verified 118132 bytes in 0.921881s (125.139 KiB/s)

> requesting target halt and executing a soft reset

> target state: halted

> target halted in ARM state due to breakpoint, current mode: Supervisor

> cpsr: 0x600000d3 pc: 0x00000000

> shutdown command invoked

>

> > Process Exit Code: 0

> > Time Taken: 00:05

●Ext12MHz,With AdaptiveClocking(RTCK),CCLK=72MHz

> > "C:/Devz/AVR/WinAVR/utils/bin/make.exe" program

> openocd -f C:/Devz/ARM/OCD/daemon.cfg -f C:/Devz/ARM/OCD/tcl/interface/jtagkey2.cfg -f C:/Devz/ARM/OCD/tcl/target/lpc2388_rclk_flash.cfg -c "mt_flash main.elf"

> Open On-Chip Debugger 0.5.0-dev-00267-gef72484 (2010-05-26-21:28)

> Licensed under GNU GPL v2

> For bug reports, read

> http://openocd.berlios.de/doc/doxygen/bugs.html

> adapter_nsrst_delay: 200

> jtag_ntrst_delay: 200

> trst_and_srst srst_pulls_trst srst_gates_jtag trst_push_pull srst_open_drain

> RCLK - adaptive

> RCLK - adaptive

> fast memory access is enabled

> dcc downloads are enabled

> Info : device: 6 "2232H"

> Info : deviceID: 67358712

> Info : SerialNumber: 22222222A

> Info : Description: Amontec JTAGkey-2 A

> Info : max TCK change to: 30000 kHz

> Info : RCLK (adaptive clock speed)

> Info : JTAG tap: lpc2388.cpu tap/device found: 0x4f1f0f0f (mfg: 0x787, part: 0xf1f0, ver: 0x4)

> Info : Embedded ICE version 7

> Error: EmbeddedICE v7 handling might be broken

> Info : lpc2388.cpu: hardware has 2 breakpoint/watchpoint units

> target state: halted

> target halted in ARM state due to debug-request, current mode: User

> cpsr: 0x60000050 pc: 0x000021bc

> flash 'lpc2000' found at 0x00000000

> auto erase enabled

> wrote 131072 bytes from file main.elf in 2.609392s (49.054 KiB/s)

> verified 118132 bytes in 0.234377s (492.212 KiB/s)

> requesting target halt and executing a soft reset

> target state: halted

> target halted in ARM state due to breakpoint, current mode: Supervisor

> cpsr: 0x600000d3 pc: 0x00000000

> shutdown command invoked

>

> > Process Exit Code: 0

> > Time Taken: 00:05

CCLKを72MHzに叩き上げたことによってベリファイ速度が滅茶苦茶速くなってます…

さすがですね〜。RAMへのダウンロードも同じくらい早いでしょう。

一方フラッシュ書き込みそのものはMAX50kb/Secで頭打ちのようです。これはフラッ

シュ消去/書き込み時間が固定でそこがボトルネックとなっているからでしょう。

STM32の方も同様の理由で頭打ちになってMAX20kB/Secが精一杯ぽいです。これももう

少し早くなると思うんだけどなあ…まだいじる必要があるのか…

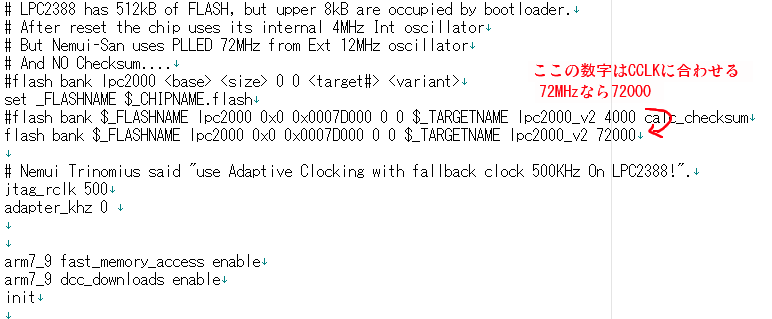

あと気をつけなければならないのがOpenOCD用スクリプトのフラッシュ書き込み時の

CCLKの設定ですが、こちらも適切な値に設定していないと正しく書きこまれません。

例としては↓こんな感じです。

RTCK対応のLPC2388用OpenOCDコンフィグは既に72MHz動作対応済みです。

そして今日はもう一件JTAGKey2Cloneを使った重要な事柄があります。

先月発売されたInterfaceには付録としてSH2Aの基板が付いていました。これにはH-UDI

とかいうJTAG用の端子が備わっていて同時期にリリースされた某JTAGデバッガを接続

してデバッグができるようになってます。"た"の人曰く最初はIF誌で同JTAGデバッガの

回路図全公開の予定だったらしいのですが大人の事情で非公開となったそうです。

でもFT2232デバイス(FT2232H)を使っているのは自明かつMPSSEでJTAGとして使える

ピンは固定なのでJTAGkey2Cloneのハードウエアが余裕で使えるんじゃないかと

言うことで実験野郎してみました。

…と思ったらすでにされてる方がいました。

てか某掲示板では動かすまでいろいろアドバイス頂きありがとうございます…。

dllをこう使えばディスクリプタ合わせるためのEEPROMの書き換えすら要らんのか…すげ

てわけでJTAGKey2Cloneまんまで動きましたワーィ

これでSPIROM何発ぶっ飛ばしても無駄な出費払わずにいつもの使って復帰できますね♥

JTAGKey2(無印やクローン含む)があればAltera,xilinx,ARM,SHの開発に使いまわせられます!

でもねむいさん国産マイコンは仕事でうんざりするほど使ってるからSH2Aとかこれ以上

触るつもり全く無いんだし!

おまけ

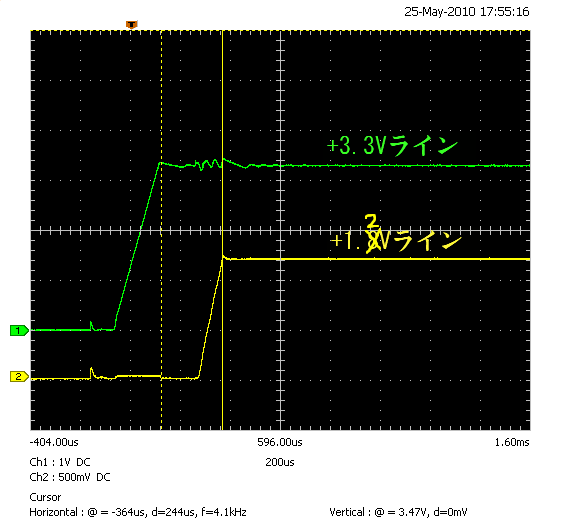

毎年気になる電源ライン

↓立ち上がり

こっちはふつーですね・・・

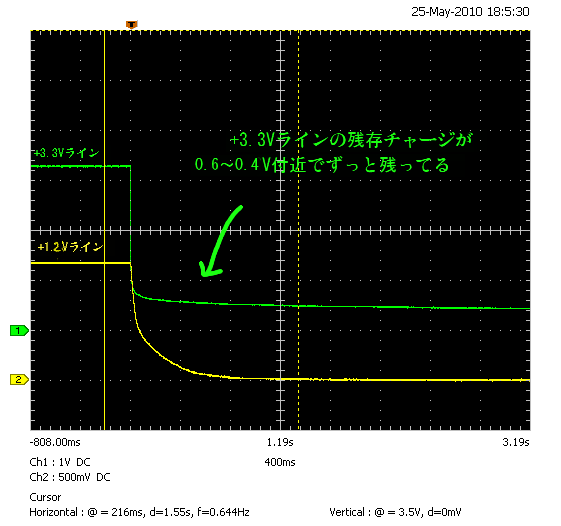

↓立ち下がり

あーっとこれは…

1.2Vはスパッと0Vまで落ちてますが3.3Vラインが0.6〜0.4V付近で長時間たむろって

ます…

リセットICの電源も+3.3Vから引いてますがこれは誤動作しやすくなるやもしれません。

1.2Vが立ちあがらないUSBが繋がらない云々の件は3.3Vラインの残存チャージが原因の

一つと見てよいですね。

対策は3.3VレギュレータのVoutからVinにチャージを引き抜くようにショットキバリア

かましてやれば良いでしょう。syslab氏もすでに試されていて実際に効果ありの

ようですね。ていうか基板設計するときにもっときっちりオシロで波け…

…まぁいいや…もうARM9のボードで遊ぼう…淘宝网で買った液晶も

たくさん残ってますし

免責・連絡先は↑のリンクを

↓SNSもやってます↓

powered by まめわざ

powered by まめわざ

- ARM/STM32 (113)

- OpenOCD (27)

- ARM/NxP (34)

- ARM/Cypress (5)

- ARM/Others (3)

- ARM/Raspi (1)

- AVR (12)

- FPGA (4)

- GPS/GNSS (19)

- MISC (79)

- STM8 (2)

- Wirelessなアレ (16)

- ブラウザベンチマーク (28)

- 日本の自然歩道 (25)

- いろいろ試す61(と今年の反省会)

⇒ ねむい (01/02) - いろいろ試す61(と今年の反省会)

⇒ ひかわ (01/02) - いろいろ試す61(と今年の反省会)

⇒ ひかわ (01/01) - STM32H5を使ってみる3 -待ち受ける初見殺しの罠たち-

⇒ ねむい (12/31) - STM32H5を使ってみる3 -待ち受ける初見殺しの罠たち-

⇒ ひかわ (12/31) - STM32H5を使ってみる3 -待ち受ける初見殺しの罠たち-

⇒ ねむい (12/28) - STM32H5を使ってみる3 -待ち受ける初見殺しの罠たち-

⇒ ひかわ (12/26) - ATTINY202(とその他)を使ってみる3 -UPDI難民問題解決の件-

⇒ ねむい (12/15) - ATTINY202(とその他)を使ってみる3 -UPDI難民問題解決の件-

⇒ 山本昌治 (11/25) - 大周回遅れでCortex-M33とSTM32L5はぢめました

⇒ ねむい (08/07)

- March 2024 (1)

- February 2024 (2)

- January 2024 (1)

- December 2023 (4)

- November 2023 (2)

- October 2023 (2)

- September 2023 (1)

- August 2023 (2)

- July 2023 (1)

- June 2023 (2)

- May 2023 (3)

- April 2023 (1)

- March 2023 (1)

- February 2023 (1)

- January 2023 (1)

- December 2022 (2)

- November 2022 (1)

- October 2022 (1)

- September 2022 (1)

- August 2022 (1)

- July 2022 (1)

- June 2022 (1)

- May 2022 (1)

- April 2022 (1)

- March 2022 (1)

- February 2022 (1)

- January 2022 (1)

- December 2021 (2)

- November 2021 (2)

- October 2021 (1)

- September 2021 (1)

- August 2021 (1)

- July 2021 (1)

- June 2021 (1)

- May 2021 (1)

- April 2021 (1)

- March 2021 (1)

- February 2021 (1)

- January 2021 (1)

- December 2020 (3)

- November 2020 (1)

- October 2020 (1)

- September 2020 (1)

- August 2020 (1)

- July 2020 (1)

- June 2020 (2)

- May 2020 (1)

- April 2020 (1)

- March 2020 (1)

- February 2020 (1)

- January 2020 (1)

- December 2019 (3)

- November 2019 (1)

- October 2019 (1)

- September 2019 (2)

- August 2019 (1)

- July 2019 (1)

- June 2019 (1)

- May 2019 (1)

- April 2019 (1)

- March 2019 (1)

- February 2019 (1)

- January 2019 (1)

- December 2018 (3)

- November 2018 (2)

- October 2018 (1)

- September 2018 (1)

- August 2018 (1)

- July 2018 (1)

- June 2018 (1)

- May 2018 (1)

- April 2018 (2)

- March 2018 (1)

- February 2018 (1)

- January 2018 (1)

- December 2017 (2)

- November 2017 (2)

- October 2017 (1)

- September 2017 (1)

- August 2017 (1)

- July 2017 (1)

- June 2017 (1)

- May 2017 (1)

- April 2017 (1)

- March 2017 (2)

- February 2017 (2)

- January 2017 (2)

- December 2016 (7)

- November 2016 (2)

- October 2016 (2)

- September 2016 (1)

- August 2016 (1)

- July 2016 (1)

- June 2016 (1)

- May 2016 (2)

- April 2016 (1)

- March 2016 (2)

- February 2016 (1)

- January 2016 (1)

- December 2015 (3)

- November 2015 (1)

- October 2015 (3)

- September 2015 (2)

- August 2015 (2)

- July 2015 (3)

- June 2015 (3)

- May 2015 (4)

- April 2015 (2)

- March 2015 (4)

- February 2015 (1)

- January 2015 (3)

- December 2014 (3)

- November 2014 (2)

- October 2014 (1)

- September 2014 (2)

- August 2014 (2)

- July 2014 (3)

- June 2014 (2)

- May 2014 (1)

- April 2014 (1)

- March 2014 (4)

- February 2014 (4)

- January 2014 (3)

- December 2013 (5)

- November 2013 (4)

- October 2013 (3)

- September 2013 (2)

- August 2013 (2)

- July 2013 (2)

- June 2013 (3)

- May 2013 (2)

- April 2013 (2)

- March 2013 (2)

- February 2013 (2)

- January 2013 (3)

- December 2012 (4)

- November 2012 (2)

- October 2012 (2)

- September 2012 (4)

- August 2012 (1)

- July 2012 (3)

- June 2012 (2)

- May 2012 (3)

- April 2012 (3)

- March 2012 (2)

- February 2012 (3)

- January 2012 (3)

- December 2011 (5)

- November 2011 (3)

- October 2011 (2)

- September 2011 (2)

- August 2011 (2)

- July 2011 (2)

- June 2011 (2)

- May 2011 (2)

- April 2011 (2)

- March 2011 (2)

- February 2011 (2)

- January 2011 (3)

- December 2010 (7)

- November 2010 (1)

- October 2010 (1)

- September 2010 (1)

- August 2010 (3)

- July 2010 (4)

- May 2010 (1)

- April 2010 (2)

- March 2010 (2)

- February 2010 (2)

- January 2010 (3)

- December 2009 (3)

- November 2009 (8)

- October 2009 (7)

- September 2009 (5)

- August 2009 (4)

- July 2009 (6)

- June 2009 (7)

- May 2009 (14)

- January 1970 (1)

Copyright(C) B-Blog project All rights reserved.

Comments

Post a Comment