LM4F120シリーズ(Stellaris Launchpad)を使ってみる

入院をごく間近というか明日に控え、プールしていた小ネタで消化します…

Launchを"らうんち"と呼んでしまうねむいさんですが注文していたのが

やっとこ手に入りました!

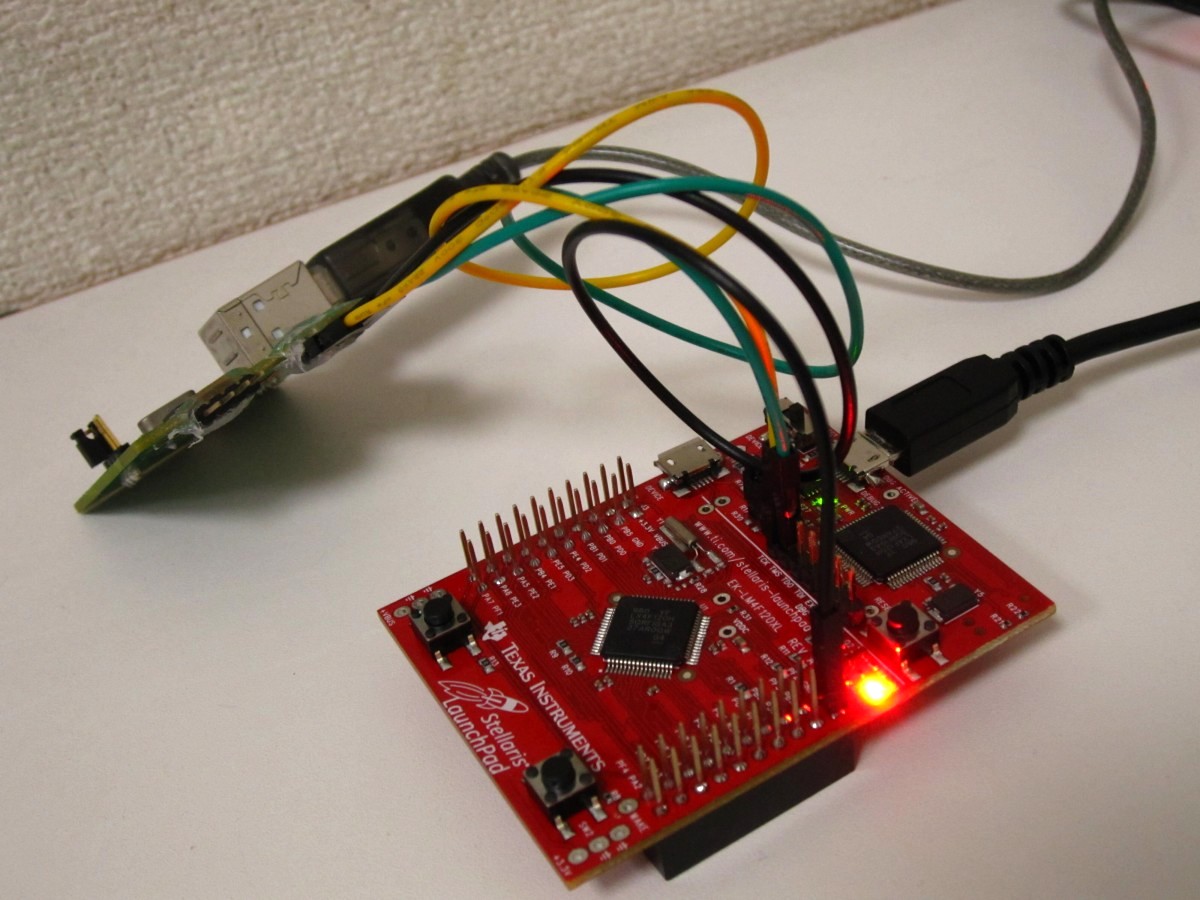

Cortex-M4Fコアが乗ったLM4F120シリーズを使った超格安評価基板である

Stellaris LM4F Launchpadです!

なんと同じチップが2つも乗っかってます。そのうちの一つはStellaris-ICDIデバッガ

ハードウエアを構成しています。

I/Oピンはプロトタイプ性を意識して亀の子が出来るコネクタが実装済です。しかし

ピン側は非常に曲がりやすいのでご注意を。

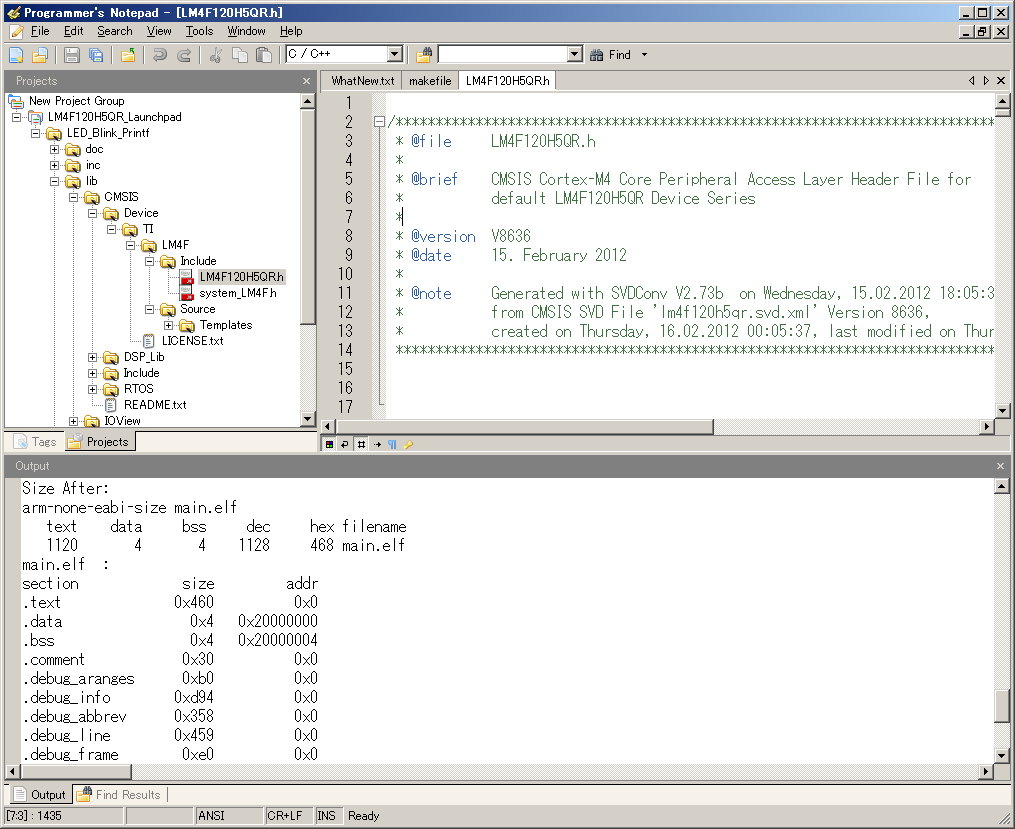

さて、取っ掛りのLED点滅を行いたいところですがStellarisWareのソースコード

だけではCMSISに準拠していないのでTIのサイトに登録し、

"TI-CMSIS-Devices-****.exe"っていう

インストーラを探してCMSIS準拠のヘッダファイルその他を取得する必要があります。

…これでSTM32等でやってたプロジェクトと同じ物が作れました。ベースはまだ

手に入れていないSTM32F3の物です…おきぱにありますので自己責任でどうぞ…

ところでビルドしたバイナリの書き込み/デバッグなのですが残念ながらLaunchpadに

付いているICDIは過去の旧Lumitaryの評価基板にあるようなFT2232系の物やそれの

エミュレーションではなく独自の物となっています。つまりまだOpenOCDにはまだ対応

していません。しかし、STによるSTLink対応の時と同じくTI側の技術者さんも協力

してくれているようで、OpenOCDへの対応は進められているようです♥

それに先立ちオープンソースのLM4Fフラッシュライタも公開されています

(コメント欄のあたり)。

また、従来のVersaloonとかのデバッガは駄目なのかというとそうでもなく、外部に出て

いるJTAGのポートにデバッガハードウエアを繋げてやればSTM32と同じくJTAG/SWDで

読み書きやデバッグが可能です!

JTAG/SWD用のヘッダピンを追加するだけで他のハンダつけ作業も不要です。

当たり前ですがStellaris特有のROMドライバの関数を使った場合、関数の

中まではいけないのでご注意を。

InsightとI/OViewでDID0レジスタを見るとLaunchpadに使われてるLM4F120H5QRの

リビジョンはRev.A3であることが分かりますね。こう言う出始めに超格安で評価

ボードバラまく時って大抵ES品とかエラッタ満載のリビジョンの浅いの乗っけるん

ですがちょっとは良心的だと思います。

↓SWD接続のVersaloonで書き込んだときのメッセージはこんな感じです。

> "C:¥Devz¥Coreutils¥bin¥make.exe" program

openocd -s C:/Devz/ARM/OCD/tcl -f interface/vsllink_swd.cfg -f target/lm4f120xxxx_flash.cfg -c "mt_flash main.elf"

Open On-Chip Debugger 0.7.0-dev-00050-g98a41bc-dirty (2012-10-18-09:39)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.sourceforge.net/doc/doxygen/bugs.html

Info : OpenOCD runs in SWD mode

adapter speed: 500 kHz

Info : Versaloon(0x15)by Simon(compiled on Jul 18 2012)

Info : USB_TO_XXX abilities: 0x0000072E:0x010001EF:0xC0000007

Info : clock speed 500 kHz

Info : lm4f120h5qr.cpu: hardware has 6 breakpoints, 4 watchpoints

adapter speed: 500 kHz

cortex_m3 reset_config sysresetreq

target state: halted

target halted due to debug-request, current mode: Thread

xPSR: 0x01000000 pc: 0x00000280 msp: 0x20008000

auto erase enabled

wrote 2048 bytes from file main.elf in 0.156251s (12.800 KiB/s)

verified 1124 bytes in 0.140626s (7.806 KiB/s)

adapter speed: 500 kHz

cortex_m3 reset_config sysresetreq

shutdown command invoked

> Process Exit Code: 0

> Time Taken: 00:01おきぱにあるOpenOCDの32bitバイナリもLM4F120系のMCUの書き込みに対応した

cfgファイルをすでに追加してあります。

FT2232系やSWD接続のVersaloonで書き込みが可能です。

Launchpad付属のICDIもあともう少し待てばOpenOCDに対応される

はずなので首を長くして待ちましょう♥

LPC4330を使ってみる3 -デュアルコアで動かす-

LPC43x0シリーズはCortex-M4FコアとCortex-M0コアが一つのチップに同時に存在する

"Heterogeneous"なデュアルコアSoCです。"某巨乳女子高生雀士のiPS細胞に関する主張

を全面支持しているねむいさんにとってはヘテロは敵にあたるわけですが早くiPSが

実用化されていないさんに私の子供をバコバコ孕まs

…ぇーっと今回はLPC4330のM4コアとM0コアを連係させて動作させてみます。

LPC4330においてはM4コア側がMaster,M0コア側がSlaveの関係となってます。

パワーオンor外部リセット直後はM0コアはリセットしっぱなし状態になっており

M4側から起こしてやることでようやくM0コアが走り始めます。

どっかの壺では全く逆のでたらめが書かれていますので注意してください。UM10503の

38pに"The IRC is selected as CPU clock and the Cortex-M4 starts the boot

loader."と明記され、さらに94pにもリセット後の各コアのステートが明記されて

おりますので必読です!

NxPのマルチコアのアプリケーションノートにも起動順がはっきりと明記されてます!

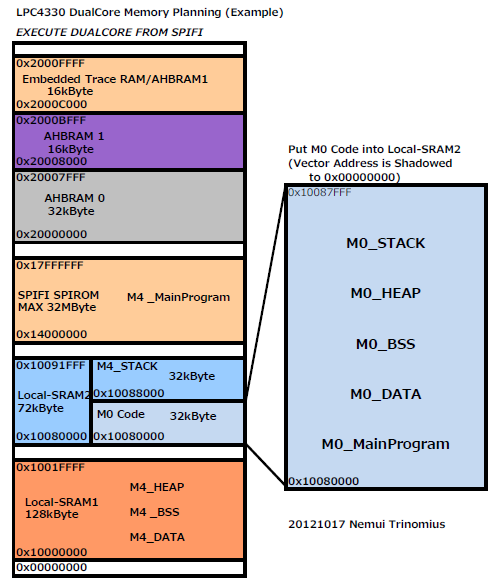

このM0コアのプログラムはどうするのかというとM4用のプログラムをビルドする

ときにM0コアのプログラムをオブジェクトとして丸々取り込み、一つのバイナリ

としてこさえる必要があります。

これを起動時に簡易なブートローダーでSRAM上にM0用プログラムを転送して、

M0コアのリセットを解除してやります。メモリ構成のイメージとしては下図の

ような感じになります。

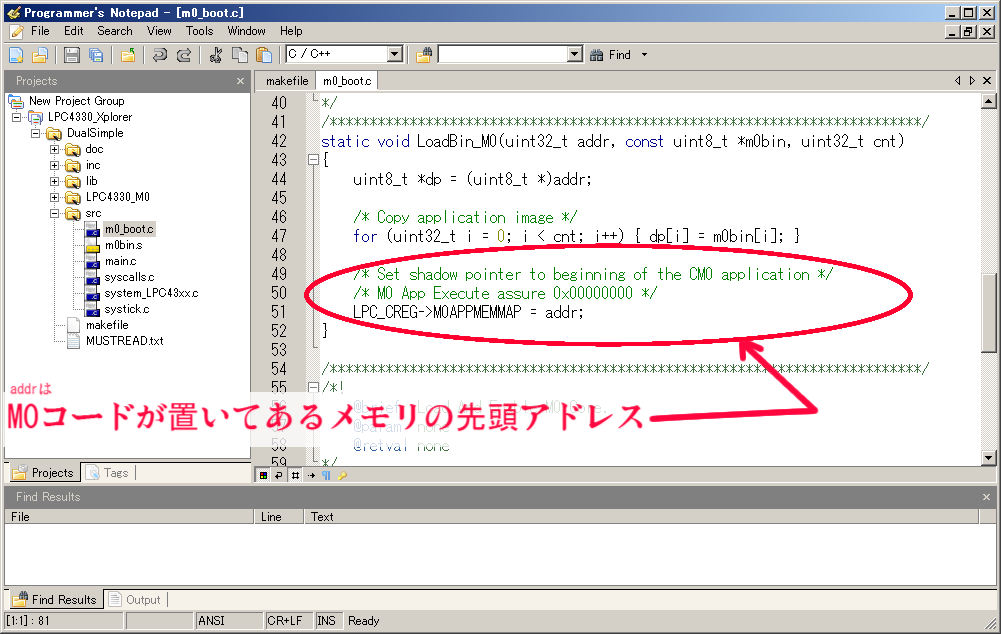

また、M0用プログラムは0x00000000にシャドウされ実行するのでM0用プログラムは

必ず0x00000000から実行するようにビルドします。それに対してスタックポインタは

実アドレスを指定しなければなりませんのでご注意を。

M0用のコードはその存在意義上小さく作りこむ必要があるので32kbyte程確保して

おけば良いでしょう。今回の例としてはLocalSRAM2の0x1008000に置きましたが、

LocalSRAM1やAHBRAMにもプログラムを置くことができます。とはいえ両方のコアを

SPIFI上ではなく、SRAM上で動かさないと本来の性能は全く引き出せず、M0コアの

ことも考えるとますます窮屈になってしまいますね。

やはりもう少しSRAM欲しかったな…204MHzでアクセスできるのが1MBくらい…。

↑M0用プログラムの転送後はM0用のベクタアドレスを設定するのを忘れずに。

ここもスタックと同じく実アドレスを指定してください。

M4コアとM0コア間の通信方法は何通りもありますが今回は公式で配布してる

サンプルに倣ってSEV命令で各コアに割り込みを発生させて通知するように

しています。

↑写真じゃよくわかりませんですけどもデュアルコアで動いてます。

今回紹介のGCCでコマンドラインビルド可能なプロジェクト一式はこちらです。

注意書きはしておりますが、M0->M4の順で必ずビルドを行ってください。

ついでですがOpenOCDのLPC4330-Xplorer向けのコンフィグファイルを少し

変更しました。

外部リセット(SRST)を一切使わずリセット制御レジスタの操作で賄うように

してます。もともとSWD接続のVerasloonで使いたかったのでSRSTがない

デバッガハードウエア向けに外部リセットを操作しないでも使えるように

するのが目的でした…が、LPC4330がデュアルコアでSWDは一つのコアにしか

対応していないの忘れていました。

結局JTAG接続専用になってしまいましたのでご注意を。

そもそもOpenOCDのspifiドライバがJTAG接続べったりの実装になってるのでぱっち当てるのめどいです

SPIFIブートにバグがあるLPC4330の動きを抑えるためのミソは以下の点です。

1.cortex-m3のリセット設定は"vectreset"にする。

2.srst/trstは"none"にする。

3.リセット信号の操作はRESET_CTRL0レジスタのCORE-Resetビットを叩く

具体的には0x40053100に0x00000001を書き100mSec程十分に待つ。

これは外部リセットとほぼ同じ効果を持ちます。

4.reset-init時にM0コアを確実にhaltさせるためにM0コアの

リセットを解除する。

具体的には0x40053104に0x00000000を書く。

これでやると外部リセットなくてもほぼうまくいきます♥

詳しい内容、使い方はlpc4330_xplorer_spifi.cfgと私のLPC4330向けプロジェクト

ファイルにあるmakefileを熟読の上。

因みにspifiブートの時に外部リセットを2度かける必要がある理由は(パワーオン時の)

リセット後の外部リセットでspifiのROMドライバにあるイニシャライズが必ずコケて

暴走するから(だからリセット後いきなりHardFaultしたように見える)で、その次の

外部リセット操作ではそれがクリアされて再々イニシャライズが成功するからだ

そうですよF**K!!!!

免責・連絡先は↑のリンクを

↓SNSもやってます↓

powered by まめわざ

powered by まめわざ

- ARM/STM32 (119)

- OpenOCD (27)

- ARM/NxP (34)

- ARM/Cypress (5)

- ARM/Others (3)

- ARM/Raspi (1)

- AVR (13)

- FPGA (4)

- GPS/GNSS (20)

- MISC (87)

- SDCard_Rumors (1)

- STM8 (2)

- Wirelessなアレ (16)

- おきぱ (1)

- ぱそこんの大先生 (2)

- ブラウザベンチマーク (31)

- 日本の自然歩道 (28)

- マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ねむい (11/24) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ひかわ (11/24) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ひかわ (11/24) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ひかわ (11/24) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ Kenji Arai (05/29) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ ねむい (05/26) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ Kenji Arai (05/24) - 中部北陸自然歩道を往く -砺波平野の県境を駆け抜ける!-

⇒ ねむい (12/18) - 中部北陸自然歩道を往く -砺波平野の県境を駆け抜ける!-

⇒ ひかわ (12/15) - STM32U0はぢめました

⇒ ねむい (08/07)

- January 2026 (1)

- December 2025 (4)

- November 2025 (1)

- October 2025 (1)

- September 2025 (1)

- August 2025 (1)

- July 2025 (1)

- June 2025 (1)

- May 2025 (1)

- April 2025 (1)

- March 2025 (1)

- February 2025 (1)

- January 2025 (1)

- December 2024 (2)

- November 2024 (1)

- October 2024 (1)

- September 2024 (1)

- August 2024 (1)

- July 2024 (1)

- June 2024 (1)

- May 2024 (1)

- April 2024 (1)

- March 2024 (1)

- February 2024 (2)

- January 2024 (1)

- December 2023 (4)

- November 2023 (2)

- October 2023 (2)

- September 2023 (1)

- August 2023 (2)

- July 2023 (1)

- June 2023 (2)

- May 2023 (3)

- April 2023 (1)

- March 2023 (1)

- February 2023 (1)

- January 2023 (1)

- December 2022 (2)

- November 2022 (1)

- October 2022 (1)

- September 2022 (1)

- August 2022 (1)

- July 2022 (1)

- June 2022 (1)

- May 2022 (1)

- April 2022 (1)

- March 2022 (1)

- February 2022 (1)

- January 2022 (1)

- December 2021 (2)

- November 2021 (2)

- October 2021 (1)

- September 2021 (1)

- August 2021 (1)

- July 2021 (1)

- June 2021 (1)

- May 2021 (1)

- April 2021 (1)

- March 2021 (1)

- February 2021 (1)

- January 2021 (1)

- December 2020 (3)

- November 2020 (1)

- October 2020 (1)

- September 2020 (1)

- August 2020 (1)

- July 2020 (1)

- June 2020 (2)

- May 2020 (1)

- April 2020 (1)

- March 2020 (1)

- February 2020 (1)

- January 2020 (1)

- December 2019 (3)

- November 2019 (1)

- October 2019 (1)

- September 2019 (2)

- August 2019 (1)

- July 2019 (1)

- June 2019 (1)

- May 2019 (1)

- April 2019 (1)

- March 2019 (1)

- February 2019 (1)

- January 2019 (1)

- December 2018 (3)

- November 2018 (2)

- October 2018 (1)

- September 2018 (1)

- August 2018 (1)

- July 2018 (1)

- June 2018 (1)

- May 2018 (1)

- April 2018 (2)

- March 2018 (1)

- February 2018 (1)

- January 2018 (1)

- December 2017 (2)

- November 2017 (2)

- October 2017 (1)

- September 2017 (1)

- August 2017 (1)

- July 2017 (1)

- June 2017 (1)

- May 2017 (1)

- April 2017 (1)

- March 2017 (2)

- February 2017 (2)

- January 2017 (2)

- December 2016 (7)

- November 2016 (2)

- October 2016 (2)

- September 2016 (1)

- August 2016 (1)

- July 2016 (1)

- June 2016 (1)

- May 2016 (2)

- April 2016 (1)

- March 2016 (2)

- February 2016 (1)

- January 2016 (1)

- December 2015 (3)

- November 2015 (1)

- October 2015 (3)

- September 2015 (2)

- August 2015 (2)

- July 2015 (3)

- June 2015 (3)

- May 2015 (4)

- April 2015 (2)

- March 2015 (4)

- February 2015 (1)

- January 2015 (3)

- December 2014 (3)

- November 2014 (2)

- October 2014 (1)

- September 2014 (2)

- August 2014 (2)

- July 2014 (3)

- June 2014 (2)

- May 2014 (1)

- April 2014 (1)

- March 2014 (4)

- February 2014 (4)

- January 2014 (3)

- December 2013 (5)

- November 2013 (4)

- October 2013 (3)

- September 2013 (2)

- August 2013 (2)

- July 2013 (2)

- June 2013 (3)

- May 2013 (2)

- April 2013 (2)

- March 2013 (2)

- February 2013 (2)

- January 2013 (3)

- December 2012 (4)

- November 2012 (2)

- October 2012 (2)

- September 2012 (4)

- August 2012 (1)

- July 2012 (3)

- June 2012 (2)

- May 2012 (3)

- April 2012 (3)

- March 2012 (2)

- February 2012 (3)

- January 2012 (3)

- December 2011 (5)

- November 2011 (3)

- October 2011 (2)

- September 2011 (2)

- August 2011 (2)

- July 2011 (2)

- June 2011 (2)

- May 2011 (2)

- April 2011 (2)

- March 2011 (2)

- February 2011 (2)

- January 2011 (3)

- December 2010 (7)

- November 2010 (1)

- October 2010 (1)

- September 2010 (1)

- August 2010 (3)

- July 2010 (4)

- May 2010 (1)

- April 2010 (2)

- March 2010 (2)

- February 2010 (2)

- January 2010 (3)

- December 2009 (3)

- November 2009 (8)

- October 2009 (7)

- September 2009 (5)

- August 2009 (4)

- July 2009 (6)

- June 2009 (6)

- May 2009 (14)

- January 1970 (1)

Copyright(C) B-Blog project All rights reserved.