SPI-ROM�λȤ�ƻ�����ޤ�����

DDT��˴������ޤޤ˹�����������դ���SPI-EEPROM��M25P40)�Ǥ�����Lattice

���Фϥ��å��Ȥ˥���ե���ROM����¢����Ƥ��뤿�ᡢ����ե���®�٤��٤�

���դ���SPI-ROM�Ϥ֤ä��㤱���֤�����ޤ������������ˡ��ispVM����

�ǤϤʤ��ȤǤ��ʤ��ΤǤ�äѤ�Ȥ�ƻ������ޤ���o�����

�Ǥ⤻�ä�����ä���ä��ΤǤ���äݤ��ȤäƤߤ뤳�Ȥˤ��ޤ����ġ�

20110527�ɡ�

ispVM��FT2232�ǥХ����������б��ˤʤ�ޤ�����

��������դ�SPIROM�ν��ߤ��ǽ�Ǥ�����

SPI-ROM�ν�����ˡ��ispVM����Ѥ�JTAG��ͳ��SPI�̿���Ԥä�

�Ԥ��櫓�Ǥ��������JTAGkey�������äƤʤ��Τ�(����ե�����SVF�Ǥ�äƤ뤷)

�����Ʊ���ε�ǽ����ĥ��եȷ�ͳ�ǽ���ɬ�פ�����ޤ���

�����������줿asagao�ϥ��Хꤽ�Τ�Τʵ�ǽ�����äƤ������

�Ȥ碌�Ƥ����������Ȥˤ��ޤ�����

�ʲ��θ������Ƥ�������ε����ǾҲ𤷤Ƥ뤳�Ȥ����ƽ���Ƥ��뤳�Ȥ�����Ǥ���

�����SPI-ROM���դ��Ȥ��褦�ˡ�

����Ū�������ˡ��asagao�Υޥ˥奢��˽��äƤ�������

�ޤ�����������LFXP2_5E�ѤΥ������å�����ե�����ϡ�

�䤬���Ǥ˺������Ƥ��ޤ��ΤǤ��������Ѥ��Ƥ���������

��USE AT YOUR OWN LISK

����ե�������ɤ߹��ߡ�"Target Device"��"CQ-FRK-LXP2"�����ꤹ��ȡ�

������JTAG�Υ������Ҥ��äƤ���о嵭���̤Τ褦��ɽ������ޤ���

"detect"�ܥ�������Ȥ�����SPI-ROM��ID���ɤߤ���ɽ���Ǥ��Ƥ��ޤ���

�����ޤǤ����餢�ȤϤ⤦����ä����꼫ͳ���ߤǤ���

���ä��åá�(���Ϲ�ʴ��)

"Erase All"�����Ȥ�����

Ŭ����hex�ե����������ǽ��ߡ���ǰ�ʤ����®��6MHz�Ǥ��٤���

���ߴ�λ��Blank Check������ȵ�ǽ���Ƥ��ޤ���

�Ĥ����SPI-ROM��̵�̤ˤ��ʤ��ƺѤߤޤ������������ĤμºݤλȤ�ƻ��

�ɤ����ޤ��礦����

����ե������Ӥ˻��Ѥ���Τ�(��¢�ե�å������٤�)�٤��������δ��Ĥ�

����ե����⡼�ɤ�������ե������CCLK���桼��I/O�Ȥ��ƻ��ѤǤ��ʤ��ʤ�

(=��ͳ��SPIROM�˥��������Ǥ��ʤ��ʤ�)�ΤǴ��Ĥ�������ƥ���ե����������

�⡼�ɤˤ��뤫���⤷����CCLK�ԥ���̤�GPIO�Ȥ�ľ�뤷�Ƥ��ɬ�פ�����ޤ���

I/O����ͭ��;�äƤ���Τ�SPI-ROM��Ȥ��ݤ��������ϸ�Ԥ���ˡ���٥��ȤǤ��礦��

DDT���Lattice���Ĥǻ�Ƥ�AVR_Core�äƤ��줫���

��ǯ�κ�������ϲ��Ƥ����ijΤ���ͤΰ����礤�������ط��ʤ�����(�����Ȥ�

���Ƥ뤱��)����2X�����Ǥ��������˼��ͤù���ǻ����ή�Ȥ��ޤ�¸�ߤ����Τ�ʤ���

"if(hoge=0)"�Ȥ�����«�Υܥ����ޤ��Ƥ�USBasp���������������������Ȥ�������������

���Ƥ�����������͎�����

�Ǥ�ޤä�����̤�и��ʻ�Ǥ⤷�ä����ӿ��路�Ƥ���Ƥ뤳�ζȳ��������餷���Ȥ��⤦�衪?

�Ǥ���ǯ���餤�ˤϻ�Ϥޤ��㤦���ǰ㤦�Ż���äƤ������ʡ��Ȥ⤪�⤦��������

��������AVR_core�ε����ˤĤ��ƥ����Ȥ����������Τǻפ��Ф����褦�ˤ�꤫����

���Τ����ĥ��Ф��Ƥ����äƤ��ޤ�����

����AVR_Core���Ȥ���ץ������Ϥ���������ñ�ʽ������ä��ΤǤ�����ư���Ƥ���

�褦�˸����ޤ�����������ʣ���ʽ���(�Ť�������)�����Ȥ��������뤳�Ȥ�ʬ�������

�����뤿�����ˡ��5��ʹߤ����������������ä�õ�äƤ��ޤ�����

��������ʬ���ä���̿Ū�ʤȤ����ϡ�ʣ���γ����ߤ�������褦�ʡ����Ȥ�������������

��Хåե��Ȥ�����ꥢ������̤Υǡ������Ǥ����ʤ��饿��������ư�����Ƥ��

�μ¤�����ˤʤ�Ȥ��������(�µ�����������ʤ�)���ͤत����Ϥ�����빦�ȸƤ��

�����ǤϤ��ξ����ˤ�������Τ���褦�˥ץ��������Ȥ�褦�˿������Ƥޤ���

����AVR_Core���ΤΥ����ɤʤΤǤ�����pm_fetch_dec.vhd��Υե饰�ν����˥Х���

���ä��餷����opencores�ˤ���ǿ��Τ�ΤǤϽ��������äƤޤ����ΤǤ�����ν�����ܿ�

���Ƥޤ��������äȤ��ʤ��ȳ����ߤȤ��ʤˤ⤫���ʤ��Ƥ�ñ�˥롼�ײƤ������

10ʬ��2~3�餤��"�ҤǤ�"���Ƥ����ǎ�����

�Ȥꤢ�����嵭2���ι�θ�Ǻ��ΤȤ����ϰ��꤫�ʡ��Ȥ��ä���Τ���äȤ��Ǥ��Ƥ����Τ�,

LPC2388���Ĥ�STM32���ĤǤ�äƤ����Ȥ�AVR_Core��ǺƸ����Ƥߤޤ�����

Chan���פ�FatFs�ʤ��Τ��������Ƥ����ΤǤ����Ĥ��Ǥ��������Ǥޤ���

������ROM:8192Byte,RAM:4096Byte�ȤäƤޤ�����(�ͤत��������̤Ǥ�)�������������

�����ɤ����꤭��ޤ������ʤ�����RAM��2kByte�˺��ROM��16kByte���������Ƥޤ���

��ǡ�RAM���Ⱥ��٤�mega103�Υ����å�����������ʤ��ʤäƤޤ��٤Ĥ����꤬����

���������������������褯�褯Ĵ�٤Ƥߤ��makefile��ǥ����å��Υ��ɥ쥹���������Ƥ�������

�褤���Ȥ�ʬ����WinAVR��°��mega103�ѤΥ������ץȤϰ��ڤ����餺�ˤ��ᤴ��

���Ȥ��Ǥ��ޤ�����

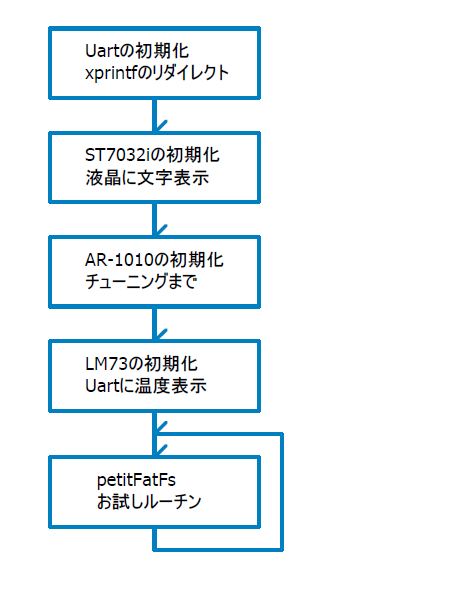

�ץ�������ή��ϲ��ޤΤȤ��ꡣ���쥭����å��Ǥ��ޤ����դ��Ƥ�LM73�Υ롼�����

�Ĥ��Ǥʤ���ͤù���ɤ��ޤ�����

���äȥ��եȥ�����i2c�ȤäƤ����ΤϤ�ȤϤȸ�����AVR_Core��i2c�ǥХ���ư���������ä�

����ȸ����Τ⤢��ޤ��ġ��褷����¢��j(ry

VHDL�Ϥ��ޤ���"--"���餤�����ޤȤ�˽���ʤ�����Lattice�δ��ĤǤ����ޤǽ��褿��������

�ȸ����櫓�Ǻ��������������Ļ�����ϼ�����Ǥ�ǡ�

�������ʹ��ĻȤ�����

���礦�Τ��ޤ�

ATMEGA32�Ǿ�Υץ������κƸ��������������ͻȤ�����

���ե�i2c��mega32��¢��i2c���������ˡ�Ǥ⥢�������Ǥ���褦�ˤ��Ƥޤ���

����AVR_Core��ͽ���Τ���˥��ե�spi�ȤäƤ��ޤ���������

�������

�⤦��Ĥ��ޤ�

�����������Ǹ�������LPC2388�Υץ����������LM73�Υ롼������ͤù���ɤ��ޤ�����

����RTC�ν����˵�������Х�(6��34���Ȥ�ɽ�������)�ȴĶ��ˤ�äƥ���ѥ��롦���顼

�ˤʤ���(ST7032i.c & rtc.c�����ʬ)�⽤�����Ƥޤ��Τǡ��������ƻ������

������������ΤϤĤ���ʤ����ʤ�٤����ä���ȤäƤۤ������♥

DDT����Ͽ��LatticeXP2���Ĥ�AVR_Core���������(�������)

���������鲼�����Ǥ��ä����äƤ��ä����ʤ�����β����쥹�Ѥγ���

�����äȻž夲��������ܿͤˤ����Ĥ����Ѥ��Ƥ�餤�ޤ�����

�פ��л䡢�Ҥ��Ӥ��˿����ܤ�����&����ͤ餷����ư���������ޤ���

���ФǤ��른���䡪�Ĥ������ڤ�֥����ι�����

��������AVR_Core��LED����&UART���ή���Υǥ�SVF�����������Ƥޤ�������

�������٤ޤȤޤ�ޤ����ΤǤ����˼����λ����Ȥ��վ�ǵ����Ƥ����ޤ���

�ͤत���夫���ɤ�Ǥ狼���٥�Τ��Ȥ��ޤ���Τǰ������餺��

�ʤޤ���������ʤ��Ǥ��줫�����ɤ�ɤ��Ѥ�롣

�֤��������ե�Ϥ��Ĥ�Ĺ���פȤ������ΰ٤��������Ϻǽ�ˤĤ��Ƥ����ޤ���

������Ǥ�Ǥɤ�����

�����ϡ��ɥ�������������ʤ��Ȥ�

��a.LatticeXP2���Ĥ�LDO&����OSC��ɬ���Ĥ��롣

����������Ȥ��ޤ������ꥢ���Ǥ��������������Τʥ����å���ɬ�פʤΤǡ�

���������å���30MHz�����(kawasan��Υ�������������4ʬ�����Ƥ�ΤǼºݤ�

����7.5MHz�Ǥ������Ƥޤ�)������ϻ䤬��äƤ�������Ǥ��ʤ���������

��b.LatticeXP2�˲��餫�μ��ʤǽ��ߤ��Ǥ���褦�ˤ��Ƥ�����

������¢�ե�å���ˤ�UrJTAG+JTAGkey��svf�ե�����κ����Ȥ�������

��������ե������Ǥ��ޤ���

����JTAGkey(�ȸߴ���ϩ)�ϻ��äƤ뤱��LPT�ݡ��Ȥ�̵��PC��ʤҤ��դ����

����78k�饤�������ѤǤ�����Ĥ���äƤʤ�&̵�̤�COM�ݡ������䤷�����ʤ�

�����ʤ�ƿͤϻ䤬��äƤ���ˡ�ǻ�ƤߤƤ���������

�������������ѤΥ��եȷ��Υ��ȡ����

����������Ȥ�館��λ��֤����뤱�ɤ���Ф졣

����äĤ���

����AVR_Core�Υ������ϡ�

��kawasan�xilinx�Ѥ˼������ߤƤ��ޤ�������Ϥ������Ȥ碌�Ƥ��ä�

��LatticeXP2�����Ȥ��Ƽ������Ƥ����ޤ���

�����ץ��������Ⱥ�äơ�

���ͤत�����ĻƬ��vhdl��ʸˡ�Ϥ⤦���ä���˺��Ƥ��ޤ��ޤ�����������

���ʤ�٤��������Ϥ�����ʤ������ǡ����Ĥ����ʤ����Τ˼����ǹԤ��ޤ�����

��(���ߥ�졼�����������ڹͤ��Ƥʤ��Ȥ����֥���ʼ�ˡ���������ɡ�)��

���ץ��������Ȥ����礷��vhd�ե����뷲�ȳ��ع�¤����������

��

����AVR¦�Υץ������ϡ�

��WINAVR(20090313)����Ѥ���ATMEGA103�ѤΥץ�������ѥ��뤷�ޤ���

����Ҥ��ޤ���RAM�ϼ¥ǥХ����Ȥۤ�Ʊ��4096�Х��ȼ��Τǥ���ѥ���¦��

���������ץȤʤɤκٹ��Ȥ���ͤ���ɬ�פ������ʤ��Ǥ���

��(cyclone���Ĥκ���DWM��˶���Ū������������Ĥʤ��ƥۥ�ȶ�ϫ����)

��kawasan���hex2vhdl.c��¹Է����ե�����ˤ��Ƥ����ơ�make��ȯ��

��prom.vhd�ޤǥץ�äȽФ�褦�ˤ��Ƥ����ޤ�����kawasan��˴��դǤ���

���ο��Υץ����������Ƥ��������ȤΤ���(�Ϥ����Ϥ����)

���Ȥꤢ��������Ȥۤ�Ʊ���ǡ�ư���Ƥޤ������٤Τ�ΤǤ���

�����Ȥˤ������������Ƥߤ�

������Ĺ����������Ĺ��������PC���ư�����Ƥ뤫�餳��ʤ�ΤʤΤǤ��礦��¿ʬ��

�������η�̤Ƥߤ��ROM��RAM���֥��å�RAM����䤷�Ƥ���Ƥޤ���

��kawasan���xilinx�ѤΤ�Τ����ΤޤȤ���褦�Ǥ���kawasan��˥ޥ����դǤ���

���������˿����Ф�

�������˰���ĥ��Ф����������ޤ�������ϺǾ��¤γ�ǧ�ʤΤ�

������ʴ���������Ҥ��ޤ���reset����ĥ��Ȥ��ϸ��Υ�������������ȿ�Ф�

���ʤäƤ�Τ����դǤ���

����jed�ե��������Ȥ�

���ԥ�������ޤǽ���ä��餳����jed���ޤ���jed����svf���������ȤΤ��ȡ�

����svf�����

��UrJTAG�ΥХå��⡼�ɤǰ쵤�ˡ�svf�ե��������erase�����äƤ����Ȥ��äȤ�

�����֤˽����Τ����ˤ�Ҥ٤��Ȥ�����

�����ȡ����٤���äƤ뤦����ʬ����ޤ��������Хå���ư������UrJTAG��detect

�������ä��Ȥ��˻��ޥե�ͤޤ�ˤʤ뤳�Ȥ��狼��ޤ���

���Хå��ε��Ҥ�detect������frequency�������2�Ҥ��Ʋ��Ƥޤ���

��(�����Ϥ��Ȥ�Ĵ�٤ޤ���)

����������������

��ư���Ƥޤ����ͤत���ȤϤۤȤ�ɲ��⤷�Ƥޤ�����ã���Ĥ��줿�����

���פ˴��դǤ��͡ġ��Ȥ����櫓�Ǥ⤦���������������Ƭ�Τ�Ʊ���Ǥ���

������Ȥ��ϼ�����Ǥ�Ǥɤ���(�귿ʸ)

�������ͻ�

��a.AVR¦�Υץ���������̤�����

�����ʤ��ͤ��ʤ��ˤ١��äȹ���������硢RAM:4096byte(����),ROM:8192byte

���������٤Ǥ������֥��å�RAM��166kbit����Τ�RAM��4096byte����ROM��

����16384byte�Ǥ⥮��Ǥ�����Ȼפ��ޤ����������ܡ�

����RAM��2048�˸��餹���̤뤫���顩�����ʤ��RAMEND��ٹ����ʤ���ʤ�ʤ�

�����ΤǤ������ʤ��ΤǤ�����

�����Ǥ⸽���������RAMROM�Ȥ����餪��λ��Ǥ���͡���

����

��b.AVR_Core¦

����kawasan���vhdl��������ʤ�٤��Ѥ��ʤ������ǹԤ��ޤ�������

����DDT����Ĥ�SW���ϥԥ��ꥻ�åȤȤ��ƻȤ��ȡ��������դˤʤäƤ��ޤ�

�����Τǥ�������ε��Ҥ��Ѥ��ޤ�����

�����ޤ���ROM���̤�8192byte�ޤǼ�ä��Τ�ROM�Υӥå������Ѥ��Ƥޤ���

����������Ĥ��ѹ�������DDT���LatticeXP2���Ĥ�AVR_Core������Ǥ��ޤ�����

��������prom.vhd�Τ���˺��Ƥ���

�ļ����Ͼ�꤯�����ޤ�������AVR_Core�Ȥ����Ϥ��ä��餬��äȤ��Ϥޤ�

�Ǥ��͡��İ��RAM&ROM���̤θ��Ѥ�꤬�Ĥ�����Ǻ�ꤿ��ʪ�Τ�ɤϤĤ��Ƥޤ���

vhdl�Ȥ�������ϩ�Ȥ��κƤ��٤�����ʤ��Τ�orz

�ǥ������롦�ǥ����ƥ��Υ�����Ͽ���Ĥ�LatticeXP2��UrJTAG+JTAGkey�ߴ���ϩ�ǥ���ե�������

2011.05.26�ɡ�

Lattice��ISPVM��FT2232�ǥХ����������б��Ȥʤ�ޤ�����

����Ǽ�ڤ��ɤ߽��Ǥ���褦�ˤʤ�ޤ���

��������Ȥʤ�ޤ�����♥

�ɤ���:

��¢Flash�˽Ȥ���.jed�ե��������ꤷ�ޤ���

SPI-ROM�˽Ȥ���.bit�ե��������ꤷ�ޤ���

����HS-1��GND����Ȥ��Ƥ������ȡ�

2009.07.31��:

Lattice����Ͽ���Ĥ�����桢���ߡ��õ���Ԥ���Ȱʸ���Ĥ�������

��ȯ����������JTAG�ǰ��ڥ��������Ǥ��ʤ��ʤ���֤˴٤��뤳�Ȥ�����ޤ���

����ϡ��Դ����ʥ���ե���->������ή�۾����->�Ű��ɥ��å�->�ƥ���ե�����

�Υ롼�פ��֤��ƥǥåɥ��å����֤˴٤äƤ뤫��Ǥ���

���ξ��֤����������ˤ�nPROG�ԥ��(Lattice���ľ��CN2_B07��)LOW��

�������ޤ��Ÿ������������Ÿ�����ľ��Υ���ե����Ϥ����ʤ����֤�

JTAG�˥���������������or�õ����������λ������ɬ�פ�����ޤ���

�����Ȥ��Ƥ��Υڡ����Υ�������������¿������ʤ��Ȥ�����2�ٸ����ޤ���

DWM�郎�Ѵ��ٴ��Ȥʤꡢ�������ǥ������롦�ǥ����ƥ��Υ�������

ά����DDT�������Ԥ���ޤ�������¿˾�ˤ�줺����°���Ĥʤ��Ĥ��Ƥޤ���

�Ф�Lattice��LFXP2-5E-5TN144C�Ǥ��͡��ե�å���١������Դ�ȯ��FPGA�Ǥ��äơ�

�ͤत�����LPC2388���ĤȽ���ARM����ư�����Τ�̴��ˤʤäƤ��Τ�

�ۤ��äƤ����Ƥ��ޤ����������������äƤߤޤ����衣LPT�ν��ߥ����ץ��Ϥ�Ϥ�

��뵤���ʤ����ʤҤ��ջ��78k��Ȥä��饤����COM�ݡ��Ȥ��������Ƥ��ޤ��ޤ���

�ͤत����Ū�ˤϥƥ��Ȥ��ͤ�UrJTAG+JTAGkey��Ȥä�SVF�ե������

�����ȸ�������Lattice�δ��Ĥ˽��ߤƸ��褦�Ȼפ��ޤ���

��5��17�����ߡ��ͥåȤǸ������Ƥ�ǥ��LED����������������

�ʳ��κ��㤬�����ȸ��äƤ����ۤɸ�������ޤ���

����ɤ�����LED���������ε�������ۤȤ�ɤʤ��Τ�������¤���ޤ���

ͣ��chan����ϥߥ���ư�����ƥ������ΰ㤤���Ĥ��Ƥ���Ƥ��ޤ�������������

������Ȥ�Ǥߤޤ�����30Mhz�ο徽��M25P40-VMN6P��LDO��ADP3339�ʤ�

�Ĥ��Ƥߤޤ��������졩����ADP3339�äơĤȤ��פ����������襤�����ˡĤ�����+5V�Ÿ���

�ؼ��ɤ������³����ȹ⤤��Ψ��ȯ����������SH2�����˾�ä��äƤ�������Ǥ��͡���

�����������"����³�����ȯ������פ����Ѥ��ʤ�"�ȸ�����ʸ���ȥåפ�����Ф�

�ȤƤ��̣���Ǥ����Ǥ�ADP3338/ADP3339�Ϥ��ʤ��衩

����Ϥ����Ȥ�������ʴ����������ʤ�������Ÿ����ưפ�æ��Ǥ���褦��

JST-XA��JTAG��ü�Ҥ�10Pin����ޤ������ºݤ˿��椬�ФƤ�Τ�

TCK,TMS,TDO,TDI,Vcc,GND�����ʤΤǡ��ϼ����Ѥ˿�����ΰ��ܤϥ��åȤ��Ƥޤ���

�Ĥ��Ǥ�9,10Pin�⥫�å�(�ǽ餫��Ĥ��ʤ���褫�ä�orz)��������Фˤʤ�8Pin���ͥ���

(�ɤ����Ĥ��9,10Pin�Ҥ��äƤʤ�����)�ϥ��åȤ���������ΰ��ܤ�

���ޤ����ϼ���¸����Ƥޤ���

ADP3339�ѤΥ���ǥ��˼������Ƥޤ���Vin�ˤ�GRM21BB31C106KE15��Vout�ˤ�

��������λ����դ���������ꤷ��+3.3V�ζ����ԤäƤ��ޤ���

����Υ��饳���+3.3V�ʲ��Υ��饳���б���LDO�Ѥ����̤���äƤ����Ƥ⤤���Ȼפ��ޤ���

��������˺��Ƥ���ADP3338/3339�Ȥ��Ȥ���RP1��RP2��ɬ������Ƥ���������

��������ͤϤ����ȥǡ��������Ȥdz�ǧ���٤���

����˺����SPIEEPROM���դ������ɰ���̵�뤹��Τ�HS1�Υ����Ѥ⥫�åȡ�

��äȤ��ʤ���SVF�ǽޤ���

��������Ͻ���ޤ����ΤǼ���svf�ե����������Ǥ��͡�

ISPLEVER�Ȥ���¾�ġ���ϥ��ȡ��뤷�Ƥ����ΤȤ����ä�ʤ�ޤ���

jed�������ޤǤϻ��̤ˤ���ΤǾʤ��ޤ��衪��

(�ġ���ȡ��뤹��ޤǰ��ϫ�Ǥ����͡���ǧ�Ĥ�館��ޤ�

���֤䤿�餫���ä��ꡢ�ޤ�����ʬ���ä��꿳�����Ƥ���Ȥ������ȤʤΤǤ��礦��

���ʤߤ˻���ȿ�̾:���ᥤ�ɶ���̾�������ꡦ�����Υߥ���̤�ޤ�����

�Ϥ¤�ƾ�ʤ����Ω�ä�(��)�ĤäƤ����Τ������)

�ǤϹԤ��ޤ��礦����

�Ȥ����櫓�Ǥ�����ü�ޤä�jed���������줿�Ȥ������饹�����ȡ�

���줫����ϲ����դ��ǡ�

��jed������������ä���ispVM��ư����

��ChainConfigration1�ȸ���������ɥ���¨���ä���

��UniversalFileWriter��ư

�������ե������SVF������

��InputDataFile�������������jed������

��RUNTEST FROM REV.C ��ON�ˤ���

��OutputDataFile̾����ꤹ�롣

��Generete�ܥ������SVF������

�Ϥ�����ޤ����͡��Ǥ��Ƥʤ��Ƥ⼡�Ԥ��ޤ���

���Ϥ��褤����ߤǤ������դ�Ĺ���ʤ�ޤ��������ä��餬���֤Ǥ���

UrJTAG�����������ɤ��ƥ��ȡ��뤷�Ƥ���������JTAGkey�����Ť������Ĥ���³����

UrJTAG��ư����������svf��UrJTAG��Ʊ���ե�������֤��ưʲ��Υ��ޥ�ɤ���֤ˡ�

�������ˡ�HS1�Υ����ѥ��å���˺��Ƥ����Ÿ���Ȥ��ƥ��åȤ��Ƥ����Ƥ͡�

>cable jtagkey

>detect(�����ȷҤ��äƤ���Ф����ǥ�����������)

>part 0

>instruction length 8

>svf (��������SVF�Υե�����̾) progress

��ʬ�ۤɤ��Ĥ�

>Scanned device output matched expected TDO values.

��ɽ�����졢FPGA�������ɤ���ޤ���

���Ⱦ����Ǥ�����svf�ե���������erase�ε��Ҥ�

>! Erase the device

>

>! Shift in ISC ERASE(0x03) instruction

>SIR 8 TDI (03);

>! wait 1.20e+002 SEC

>RUNTEST IDLE 120000003 TCK;

��

>RUNTEST IDLE 120000003 TCK;

��

>RUNTEST IDLE 5000003 TCK;

���餤�˸��餷�Ƥ��Ƚ����֤�������û�̤Ǥ��ޤ���

��®��40�ä��餤�ǥ���ե����Ǥ��ޤ������줾��δĶ���Ĵ�����Ƹ��Ƥ���������

�ޤ����⤷���ߤ����Ԥ���FPGA������ʾ��֤˴٤ä���nPROG�ԥ��(���ľ��

CN2_B07��)LOW�˰������ޤ��Ÿ����������ƺƤӽ��ߤ�ԤäƲ�������

���������͡����ļΤƤ�ͤ�������������ʣ�����(��������ͺ����)

����ʤ��ä��뤤���ޥ�����Ϥ���������äƤ��뤫�����ȸ���

���ϥХå��Ǽ¹Ԥ��������⤢��ޤ��ΤǤ��Ҳ𤷤ޤ���

����������˥���ץ��դ��Ǥ���ޤ��Τ���Υե����븫�Ƥͤत����

��������������Ǥ���ͤ���������Ǥ�Ǥɤ�����

30MHz�γ���OSCɬ�ܤǤ����Ǥ�UART�פ�ʤ��ͤ��ä˼��ȿ��˵��ˤ��ʤ��Ƥ⤤���Ǥ���

���ա�Ϣ����Ϣ��Υ��

��SNS���äƤޤ���

powered by �ޤ�虜

powered by �ޤ�虜

- ARM/STM32 (119)

- OpenOCD (27)

- ARM/NxP (34)

- ARM/Cypress (5)

- ARM/Others (3)

- ARM/Raspi (1)

- AVR (13)

- FPGA (4)

- GPS/GNSS (20)

- MISC (86)

- SDCard_Rumors (1)

- STM8 (2)

- Wireless�ʥ��� (16)

- ������ (1)

- �֥饦���٥���ޡ��� (29)

- ���ܤμ�����ƻ (27)

- GNSS�⥸�塼�����Ѥ���21 -SAM-M10Q�����줿��!?�Ȼפä���ľ����(���ޤ�����)-

�� Kenji Arai (05/29) - GNSS�⥸�塼�����Ѥ���21 -SAM-M10Q�����줿��!?�Ȼפä���ľ����(���ޤ�����)-

�� �ͤत (05/26) - GNSS�⥸�塼�����Ѥ���21 -SAM-M10Q�����줿��!?�Ȼפä���ľ����(���ޤ�����)-

�� Kenji Arai (05/24) - ������Φ������ƻ����� -����ʿ��θ�����ȴ���롪-

�� �ͤत (12/18) - ������Φ������ƻ����� -����ʿ��θ�����ȴ���롪-

�� �Ҥ��� (12/15) - STM32U0�Ϥ¤�ޤ���

�� �ͤत (08/07) - STM32U0�Ϥ¤�ޤ���

�� �Ҥ��� (07/28) - STM32H5��ȤäƤߤ�3 -�Ԥ�������鸫������櫤���-

�� �ͤत (05/17) - STM32H5��ȤäƤߤ�3 -�Ԥ�������鸫������櫤���-

�� �ɤ����� (05/16) - STM32H5��ȤäƤߤ�3 -�Ԥ�������鸫������櫤���-

�� �ɤ����� (05/16)

- October 2025 (1)

- September 2025 (1)

- August 2025 (1)

- July 2025 (1)

- June 2025 (1)

- May 2025 (1)

- April 2025 (1)

- March 2025 (1)

- February 2025 (1)

- January 2025 (1)

- December 2024 (2)

- November 2024 (1)

- October 2024 (1)

- September 2024 (1)

- August 2024 (1)

- July 2024 (1)

- June 2024 (1)

- May 2024 (1)

- April 2024 (1)

- March 2024 (1)

- February 2024 (2)

- January 2024 (1)

- December 2023 (4)

- November 2023 (2)

- October 2023 (2)

- September 2023 (1)

- August 2023 (2)

- July 2023 (1)

- June 2023 (2)

- May 2023 (3)

- April 2023 (1)

- March 2023 (1)

- February 2023 (1)

- January 2023 (1)

- December 2022 (2)

- November 2022 (1)

- October 2022 (1)

- September 2022 (1)

- August 2022 (1)

- July 2022 (1)

- June 2022 (1)

- May 2022 (1)

- April 2022 (1)

- March 2022 (1)

- February 2022 (1)

- January 2022 (1)

- December 2021 (2)

- November 2021 (2)

- October 2021 (1)

- September 2021 (1)

- August 2021 (1)

- July 2021 (1)

- June 2021 (1)

- May 2021 (1)

- April 2021 (1)

- March 2021 (1)

- February 2021 (1)

- January 2021 (1)

- December 2020 (3)

- November 2020 (1)

- October 2020 (1)

- September 2020 (1)

- August 2020 (1)

- July 2020 (1)

- June 2020 (2)

- May 2020 (1)

- April 2020 (1)

- March 2020 (1)

- February 2020 (1)

- January 2020 (1)

- December 2019 (3)

- November 2019 (1)

- October 2019 (1)

- September 2019 (2)

- August 2019 (1)

- July 2019 (1)

- June 2019 (1)

- May 2019 (1)

- April 2019 (1)

- March 2019 (1)

- February 2019 (1)

- January 2019 (1)

- December 2018 (3)

- November 2018 (2)

- October 2018 (1)

- September 2018 (1)

- August 2018 (1)

- July 2018 (1)

- June 2018 (1)

- May 2018 (1)

- April 2018 (2)

- March 2018 (1)

- February 2018 (1)

- January 2018 (1)

- December 2017 (2)

- November 2017 (2)

- October 2017 (1)

- September 2017 (1)

- August 2017 (1)

- July 2017 (1)

- June 2017 (1)

- May 2017 (1)

- April 2017 (1)

- March 2017 (2)

- February 2017 (2)

- January 2017 (2)

- December 2016 (7)

- November 2016 (2)

- October 2016 (2)

- September 2016 (1)

- August 2016 (1)

- July 2016 (1)

- June 2016 (1)

- May 2016 (2)

- April 2016 (1)

- March 2016 (2)

- February 2016 (1)

- January 2016 (1)

- December 2015 (3)

- November 2015 (1)

- October 2015 (3)

- September 2015 (2)

- August 2015 (2)

- July 2015 (3)

- June 2015 (3)

- May 2015 (4)

- April 2015 (2)

- March 2015 (4)

- February 2015 (1)

- January 2015 (3)

- December 2014 (3)

- November 2014 (2)

- October 2014 (1)

- September 2014 (2)

- August 2014 (2)

- July 2014 (3)

- June 2014 (2)

- May 2014 (1)

- April 2014 (1)

- March 2014 (4)

- February 2014 (4)

- January 2014 (3)

- December 2013 (5)

- November 2013 (4)

- October 2013 (3)

- September 2013 (2)

- August 2013 (2)

- July 2013 (2)

- June 2013 (3)

- May 2013 (2)

- April 2013 (2)

- March 2013 (2)

- February 2013 (2)

- January 2013 (3)

- December 2012 (4)

- November 2012 (2)

- October 2012 (2)

- September 2012 (4)

- August 2012 (1)

- July 2012 (3)

- June 2012 (2)

- May 2012 (3)

- April 2012 (3)

- March 2012 (2)

- February 2012 (3)

- January 2012 (3)

- December 2011 (5)

- November 2011 (3)

- October 2011 (2)

- September 2011 (2)

- August 2011 (2)

- July 2011 (2)

- June 2011 (2)

- May 2011 (2)

- April 2011 (2)

- March 2011 (2)

- February 2011 (2)

- January 2011 (3)

- December 2010 (7)

- November 2010 (1)

- October 2010 (1)

- September 2010 (1)

- August 2010 (3)

- July 2010 (4)

- May 2010 (1)

- April 2010 (2)

- March 2010 (2)

- February 2010 (2)

- January 2010 (3)

- December 2009 (3)

- November 2009 (8)

- October 2009 (7)

- September 2009 (5)

- August 2009 (4)

- July 2009 (6)

- June 2009 (6)

- May 2009 (14)

- January 1970 (1)

Copyright(C) B-Blog project All rights reserved.