DDT誌のLattice基板で試してたAVR_Coreってあれから…

去年の今頃、私は何をしてたか…確か主人の引き合いで全く関係ない職種(今も兼業で

してるけど)から2Xさいでこの世界に首突っ込んで三相交流とかまだ存在すら知らなくて

"if(hoge=0)"とかお約束のボケかましててUSBaspすげぇぇぇぇぇぇぇぇとかいちいち感心

してたころかしらね・・・

でもまったくの未経験な私でもしっかり飯食わしてくれてるこの業界は素晴らしいとおもうよ!?

でも来年くらいには私はまた違う場所で違う仕事やってるんだろなーともおもう・・・。

少し前にAVR_coreの記事についてコメントいただいたので思い出したようにやりかけて

たのを引っ張り出していじっていました。

以前AVR_Coreで組んだプログラムはごくごく簡単な処理だったのでちゃんと動いている

ように見えましたが、少し複雑な処理(重たい処理)をしだすとすぐコケることが分かり安定

させるための方法を5月以降ず〜〜〜〜〜〜〜っと探っていました。

現時点で分かった致命的なところは、複数の割り込みがかかるような、たとえば送信受信の

リングバッファ組んだシリアルで大量のデータを吐かせながらタイマ割り込み動かしてると

確実に不安定になるという問題で(実機は全く問題なし)、ねむいさんはこれを秘孔と呼んで

現状ではこの状況におちいるのを避けるようにプログラムを組むように心がけてます。

次にAVR_Core本体のコードなのですが…pm_fetch_dec.vhd内のフラグの処理にバグが

あったらしく、opencoresにある最新のものでは修正が入ってましたのでこちらの修正を移植

してます。これやっとかないと割り込みとかなにもかけなくても単にループ回してるだけで

10分に2~3回くらいは"ひでぶ"してたもんで・・・

とりあえず上記2点の考慮で今のところは安定かな?といったものがやっとこできてきたので,

LPC2388基板やSTM32基板でやってたことをAVR_Core上で再現してみました。

ChanさんがぷちFatFsなるものを公開されていたのでこれもついでに盛り込んでます。

以前はROM:8192Byte,RAM:4096Byteとってましたが(ねむいさんの力量では)こんだけ入れると

コードが入りきりません。仕方ないもんでRAMを2kByteに削りROMを16kByteに増強してます。

んで、RAM削ると今度はmega103のスタックの定義が合わなくなってまたべつの問題ががg

・・・・・・しかし、よくよく調べてみるとmakefile内でスタックのアドレスを明示してやるだけで

よいことが分かりWinAVR付属のmega103用のリンカスクリプトは一切いじらずにやり過ごす

ことができました。

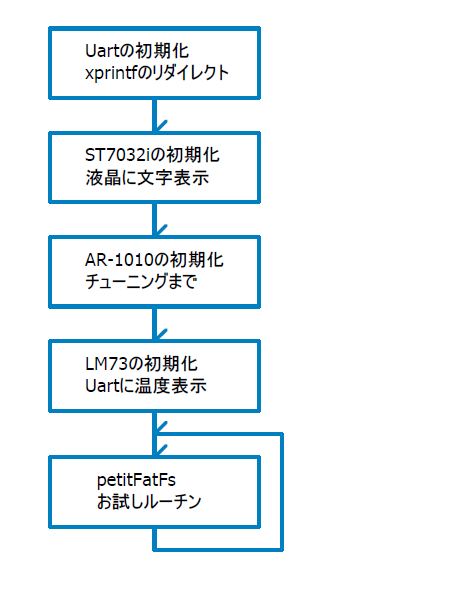

プログラムの流れは下図のとおり。エレキジャックでおまけに付いてたLM73のルーチンも

ついでなんで突っ込んどきました。

ずっとソフトウエアi2c使ってきたのはもとはと言えばAVR_Coreでi2cデバイス動かしたかった

からと言うのもあります…。決して内蔵レj(ry

VHDLはいまだに"--"くらいしかまともに出来ないけどLatticeの基板でここまで出来たぞー!!

と言うわけで今日のおソース…試される場合は自己責任で…

そうだね基板使い回しだね

きょうのおまけ

ATMEGA32で上のプログラムの再現・・・そうだね使い回しだね

ソフトi2cとmega32内蔵のi2cいずれの方法でもアクセスできるようにしてます。

あとAVR_Coreの予習のためにソフトspi使っています・・・。

こちらに

もう一つおまけ

先日の日記で公開したLPC2388のプログラムの中にLM73のルーチンも突っ込んどきました。

あとRTCの処理に起因するバグ(6月34日とか表示される)と環境によってコンパイル・エラー

になる場所(ST7032i.c & rtc.c内の部分)も修正してますので、真似して試される場合は

前回公開したのはつかわないでなるべくこっちを使ってほしいんだ♥

免責・連絡先は↑のリンクを

↓SNSもやってます↓

powered by まめわざ

powered by まめわざ

- ARM/STM32 (119)

- OpenOCD (27)

- ARM/NxP (34)

- ARM/Cypress (5)

- ARM/Others (3)

- ARM/Raspi (1)

- AVR (13)

- FPGA (4)

- GPS/GNSS (20)

- MISC (87)

- SDCard_Rumors (2)

- STM8 (2)

- Wirelessなアレ (16)

- おきぱ (1)

- ぱそこんの大先生 (2)

- ブラウザベンチマーク (31)

- 日本の自然歩道 (28)

- SDカードとかUSBメモリにSystem Volume Information絶対作らせなくする方法Win11版

⇒ ねむい (01/28) - SDカードとかUSBメモリにSystem Volume Information絶対作らせなくする方法Win11版

⇒ (01/28) - SDカードとかUSBメモリにSystem Volume Information絶対作らせなくする方法Win11版

⇒ (01/28) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ねむい (11/24) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ひかわ (11/24) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ひかわ (11/24) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ひかわ (11/24) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ Kenji Arai (05/29) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ ねむい (05/26) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ Kenji Arai (05/24)

- February 2026 (1)

- January 2026 (1)

- December 2025 (4)

- November 2025 (1)

- October 2025 (1)

- September 2025 (1)

- August 2025 (1)

- July 2025 (1)

- June 2025 (1)

- May 2025 (1)

- April 2025 (1)

- March 2025 (1)

- February 2025 (1)

- January 2025 (1)

- December 2024 (2)

- November 2024 (1)

- October 2024 (1)

- September 2024 (1)

- August 2024 (1)

- July 2024 (1)

- June 2024 (1)

- May 2024 (1)

- April 2024 (1)

- March 2024 (1)

- February 2024 (2)

- January 2024 (1)

- December 2023 (4)

- November 2023 (2)

- October 2023 (2)

- September 2023 (1)

- August 2023 (2)

- July 2023 (1)

- June 2023 (2)

- May 2023 (3)

- April 2023 (1)

- March 2023 (1)

- February 2023 (1)

- January 2023 (1)

- December 2022 (2)

- November 2022 (1)

- October 2022 (1)

- September 2022 (1)

- August 2022 (1)

- July 2022 (1)

- June 2022 (1)

- May 2022 (1)

- April 2022 (1)

- March 2022 (1)

- February 2022 (1)

- January 2022 (1)

- December 2021 (2)

- November 2021 (2)

- October 2021 (1)

- September 2021 (1)

- August 2021 (1)

- July 2021 (1)

- June 2021 (1)

- May 2021 (1)

- April 2021 (1)

- March 2021 (1)

- February 2021 (1)

- January 2021 (1)

- December 2020 (3)

- November 2020 (1)

- October 2020 (1)

- September 2020 (1)

- August 2020 (1)

- July 2020 (1)

- June 2020 (2)

- May 2020 (1)

- April 2020 (1)

- March 2020 (1)

- February 2020 (1)

- January 2020 (1)

- December 2019 (3)

- November 2019 (1)

- October 2019 (1)

- September 2019 (2)

- August 2019 (1)

- July 2019 (1)

- June 2019 (1)

- May 2019 (1)

- April 2019 (1)

- March 2019 (1)

- February 2019 (1)

- January 2019 (1)

- December 2018 (3)

- November 2018 (2)

- October 2018 (1)

- September 2018 (1)

- August 2018 (1)

- July 2018 (1)

- June 2018 (1)

- May 2018 (1)

- April 2018 (2)

- March 2018 (1)

- February 2018 (1)

- January 2018 (1)

- December 2017 (2)

- November 2017 (2)

- October 2017 (1)

- September 2017 (1)

- August 2017 (1)

- July 2017 (1)

- June 2017 (1)

- May 2017 (1)

- April 2017 (1)

- March 2017 (2)

- February 2017 (2)

- January 2017 (2)

- December 2016 (7)

- November 2016 (2)

- October 2016 (2)

- September 2016 (1)

- August 2016 (1)

- July 2016 (1)

- June 2016 (1)

- May 2016 (2)

- April 2016 (1)

- March 2016 (2)

- February 2016 (1)

- January 2016 (1)

- December 2015 (3)

- November 2015 (1)

- October 2015 (3)

- September 2015 (2)

- August 2015 (2)

- July 2015 (3)

- June 2015 (3)

- May 2015 (4)

- April 2015 (2)

- March 2015 (4)

- February 2015 (1)

- January 2015 (3)

- December 2014 (3)

- November 2014 (2)

- October 2014 (1)

- September 2014 (2)

- August 2014 (2)

- July 2014 (3)

- June 2014 (2)

- May 2014 (1)

- April 2014 (1)

- March 2014 (4)

- February 2014 (4)

- January 2014 (3)

- December 2013 (5)

- November 2013 (4)

- October 2013 (3)

- September 2013 (2)

- August 2013 (2)

- July 2013 (2)

- June 2013 (3)

- May 2013 (2)

- April 2013 (2)

- March 2013 (2)

- February 2013 (2)

- January 2013 (3)

- December 2012 (4)

- November 2012 (2)

- October 2012 (2)

- September 2012 (4)

- August 2012 (1)

- July 2012 (3)

- June 2012 (2)

- May 2012 (3)

- April 2012 (3)

- March 2012 (2)

- February 2012 (3)

- January 2012 (3)

- December 2011 (5)

- November 2011 (3)

- October 2011 (2)

- September 2011 (2)

- August 2011 (2)

- July 2011 (2)

- June 2011 (2)

- May 2011 (2)

- April 2011 (2)

- March 2011 (2)

- February 2011 (2)

- January 2011 (3)

- December 2010 (7)

- November 2010 (1)

- October 2010 (1)

- September 2010 (1)

- August 2010 (3)

- July 2010 (4)

- May 2010 (1)

- April 2010 (2)

- March 2010 (2)

- February 2010 (2)

- January 2010 (3)

- December 2009 (3)

- November 2009 (8)

- October 2009 (7)

- September 2009 (5)

- August 2009 (4)

- July 2009 (6)

- June 2009 (6)

- May 2009 (14)

- January 1970 (1)

Copyright(C) B-Blog project All rights reserved.

Comments

yaccです。

AVRコアのアップデート拝見しました。

私の方はまだIPコア探しの旅の途中です。

AVRマイコンは使い慣れているのですが、残念ながらverilogな人なのでVHDLで記述されているコアは使い辛いのです。

今は一周回ってMico8に再チャレンジしています。

所で、CPUコアをFPGAにいれて利用する時に困るのがプログラムのデバッグです。

AVRコアも合成に恐ろしく時間がかかるので、ちょっとしたプログラム修正でもすごく時間が必要になります。

ねむいさんはどのようにされていますか?

ispLEVERにはMemory Initializing Toolというのがあって、再合成を行わずにncdファイルの中のメモリの初期値を変更できるようです。このツールを使用するにはROMをIP Expressで生成して、Latticeの指定しているメモリ初期値ファイルで初期化しておかないといけないと思います。

こんばんは。ねむいです。

ソフトCPUの論理合成は確かにものすごく時間かかりますね…AVR_Core"も"と

言うことはLatticeお抱えのMico8もやっぱし合成にそれなりの時間がかかると

いうことですか…

もうご存知かと思いますが、OPENCORESにある最新のAVR_CoreはJTAGインターフェース

を備え、ROMとして論理合成されたブロックRAMの領域にJTAGICE等の既成のツールで

プログラムの書き込みができるようになっています。

残念ながらDDT誌の基板にはそれを載せるに足る資源がないので、結局合成に

メタクソ時間がかかる古いほうのコードでせこせこやっていますorz

論理合成中は空いた時間利用してATmega32(実機)で動作の予習したりしてました。

Memory Initializing Tool使う方法はまだまったく試してないので、使い物になるか

どうか少し調査してみます。少しでも時間の短縮につながればよいですね〜。

それとAVR_Coreをverilogへのトランスレータを行われてる方がいました。

ttp://japanese.sugawara-systems.com/opencores/benchmark/benchmark_AVR.htm

ご参考までに…

AVRコアは今はJTAG経由でプログラムの書き換えが出来るのですか…

勉強不足で知りませんでした。

JTAGのコードが入らないのであれば、Memory Initializing Toolを是非活用して下さい。デバッグ効率がずいぶん上がるはずですよ。

Mico8は小さいので合成も数分で終わります。それでもプログラムを書き換えるたびに合成するのは避けたいですね。

AlteraのFPGAにも同様の機能があり、以前にAVRコアを実装した時に利用しました。

#ええ、以前にもAVR_Coreを使った事があるのですよ。今、古いファイルを探したら2003年の日付でした。

#途中で投げ出しちゃったような記憶があるので、知らないのと同じです。

#もしかしたら、ご指摘のバグがあったのかも。ちょっと複雑なプログラムを書くと変な動作をしていたような気がします。

Xilinxはあまり使用経験がないのですが、PicoblazeというCPUコアにはJTAG経由でプログラムを変更する追加機能(AVR_Coreと同じ方式ですね)がありました。

Mico8の方は、シミュレーションが動きはじめました。

branch命令でとんでもない所にジャンプしているようです。

もうちょっと頑張ります。

ねむいです。こんばんは。

LatticeのMemory Initializing Toolを使う方法、(VHDLの勉強をしつつ)進展があったら

また日記に書かせてもらいますね〜。

yaccさんが行われているMico8の検証もうまく行くようご武運を祈っております…。

Post a Comment