STM32H5を使ってみる2 -フラッシュ書き込み&デバッグ環境作るだけで疲労困憊-

20240516追:

秋月さんよりNUCLEO-H563ZI販売開始です!!

20240516追:

秋の登山ラッシュに入ってしまったのでせっかく買ったのに全く

STM32H5触れてない毎日ですがわずかな時間を見つけてすこしでも

進ませていただきます!!!

さて今回からSTM32L5で行ったように基本となる機能と開発環境の

確認を紹介していきます。

●OpenOCDがSTM32H5に対応してない!?大丈夫だ問題ない

はい、ヒ改めメのタイムライン見てもSTM32H5の話題が全く上がらず盛り上がって

ないのはこれが原因かと思われます。

OpenOCDのメーリングリストではH5試したけどL5みたいに動かないよー

というアーリーアダプタの方のコメントがありますがその後の進展は

全くなし…。

幸いにもSTマイクロ公式でForkしているOpenOCDのgitではひっそりと

STM32H5に対応しておりますがこちらも今年春から進展はなく、OpenOCD

本家の主流から大きく引き離されております。

とりあえずですがSTマイクロのソースコードを分析して最新のOpenOCD

でもビルド・動作できるようにしたものをねむいさんのおきぱに配置

しておりますのでご利用ください…

ところでL5とH5は同じCortex-M33コアなのになぜここまで違うのか?

という疑問ですがコアのrevid,devidを取得する関数が大幅に違います。

・STM32H5

static int stm32h5x_read_idcode(struct flash_bank *bank, uint32_t *id)

{

struct target *target = bank->target;

struct cortex_m_common *cortex_m = target_to_cm(bank->target);

struct adiv5_ap *ap = cortex_m->armv7m.debug_ap;

/* DBGMCU_IDCODE cannot be read from AP1, read it from ROM Table */

target_addr_t dbgbase;

uint32_t apid;

int retval = dap_get_debugbase(ap, &dbgbase, &apid);

if (retval != ERROR_OK)

return retval;

target_addr_t base_addr = dbgbase & 0xFFFFFFFFFFFFF000ull;

/* PID Registers 0 to 3 are sufficient to identify the device */

uint32_t pid_regs[4];

retval = target_read_memory(target, base_addr + ARM_CS_PIDR0, 4, 4, (uint8_t *)pid_regs);

if (retval != ERROR_OK)

return retval;

uint64_t pid = (pid_regs[3] & 0xff) << 24

| (pid_regs[2] & 0xff) << 16

| (pid_regs[1] & 0xff) << 8

| (pid_regs[0] & 0xff);

uint16_t dev_id = pid & 0x0FFF;

uint8_t rev_id_major = pid >> 20 & 0xF;

uint8_t rev_id_minor = pid >> 28 & 0xF;

uint16_t rev_id = rev_id_major << 12 | rev_id_minor;

*id = rev_id << 16 | dev_id;

return retval;

}・STM32L5たち

static int stm32l4_read_idcode(struct flash_bank *bank, uint32_t *id)

{

int retval = ERROR_OK;

struct target *target = bank->target;

/* try reading possible IDCODE registers, in the following order */

uint32_t dbgmcu_idcode[] = {DBGMCU_IDCODE_L4_G4, DBGMCU_IDCODE_L5, DBGMCU_IDCODE_G0};

for (unsigned int i = 0; i < ARRAY_SIZE(dbgmcu_idcode); i++) {

retval = target_read_u32(target, dbgmcu_idcode[i], id);

if ((retval == ERROR_OK) && ((*id & 0xfff) != 0) && ((*id & 0xfff) != 0xfff))

return ERROR_OK;

}

/* Workaround for STM32WL5x devices:

* DBGMCU_IDCODE cannot be read using CPU1 (Cortex-M0+) at AP1,

* to solve this read the UID64 (IEEE 64-bit unique device ID register) */

struct armv7m_common *armv7m = target_to_armv7m_safe(target);

if (!armv7m) {

LOG_ERROR("Flash requires Cortex-M target");

return ERROR_TARGET_INVALID;

}

/* CPU2 (Cortex-M0+) is supported only with non-hla adapters because it is on AP1.

* Using HLA adapters armv7m.debug_ap is null, and checking ap_num triggers a segfault */

if (cortex_m_get_partno_safe(target) == CORTEX_M0P_PARTNO &&

armv7m->debug_ap && armv7m->debug_ap->ap_num == 1) {

uint32_t uid64_ids;

/* UID64 is contains

* - Bits 63:32 : DEVNUM (unique device number, different for each individual device)

* - Bits 31:08 : STID (company ID) = 0x0080E1

* - Bits 07:00 : DEVID (device ID) = 0x15

*

* read only the fixed values {STID,DEVID} from UID64_IDS to identify the device as STM32WLx

*/

retval = target_read_u32(target, UID64_IDS, &uid64_ids);

if (retval == ERROR_OK && uid64_ids == UID64_IDS_STM32WL) {

/* force the DEV_ID to DEVID_STM32WLE_WL5XX and the REV_ID to unknown */

*id = DEVID_STM32WLE_WL5XX;

return ERROR_OK;

}

}

LOG_ERROR("can't get the device id");

return (retval == ERROR_OK) ? ERROR_FAIL : retval;

}注:STM32L5のフラッシュ書き込みのコードはstm32l4x.cに取り込まれてます。

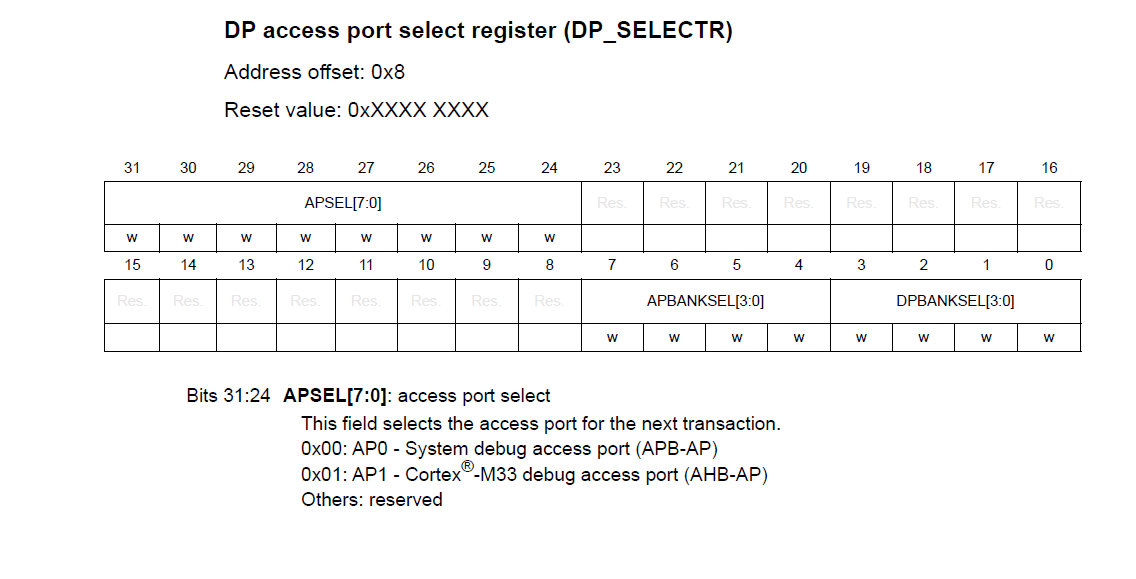

本来ならSTM32L5と同じくDBGMCU_IDCODEレジスタ(0xE0044000)から

読んでくれば終わる話なのですがSTM32H5ではそれができません。

DBGMCU_IDCODEがあるAHB-AP(AP1)から読もうとすると0しか返ってきません。

仕方ないのでAP0にあるROMTABLEからPID0~3を読みだしてdevid,revidを

読みだす必要があるわけです。んなことわかるか!!!

さて、何とかSTM32H5対応なおかつ最新のコミットにOpenOCDを対応させ

書き込みしてみたログは以下のようになりました。

書き込みスクリプトはねむいさん謹製のstm32h5x_flash.cfgを使用します。

> "C:¥Devz¥Coreutils¥bin¥make.exe" program

openocd -s C:/Devz/ARM/OCD/tcl -f interface/stlink-dap.cfg -c "transport select dapdirect_swd" -f target/stm32h5x_flash.cfg -c "mt_flash main.elf"

Open On-Chip Debugger 0.12.0+dev-00415-gacde409ba (2023-11-23-16:02)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

dapdirect_swd

Info : STLINK V3J13M4 (API v3) VID:PID 0483:3754

Info : Target voltage: 3.278828

Info : Unable to match requested speed 480 kHz, using 200 kHz

Info : Unable to match requested speed 480 kHz, using 200 kHz

Info : clock speed 200 kHz

Info : stlink_dap_op_connect(connect)

Info : SWD DPIDR 0x6ba02477

Info : [stm32h5x.cpu] Cortex-M33 r0p4 processor detected

Info : [stm32h5x.cpu] target has 8 breakpoints, 4 watchpoints

Info : starting gdb server for stm32h5x.cpu on 3333

Info : Listening on port 3333 for gdb connections

Info : Unable to match requested speed 480 kHz, using 200 kHz

Info : Unable to match requested speed 480 kHz, using 200 kHz

CPU in Non-Secure state

[stm32h5x.cpu] halted due to debug-request, current mode: Thread

xPSR: 0xf9000000 pc: 0x08030dac msp: 0x20050000

Info : Unable to match requested speed 4000 kHz, using 3300 kHz

Info : Unable to match requested speed 4000 kHz, using 3300 kHz

Info : device idcode = 0x10000484 (STM32H56/H57xx - Rev A : 0x1000)

Info : TZEN = 0xC3 : TrustZone disabled by option bytes

Info : Product State = 0xED : 'Open'

Info : flash size = 2048kbytes

Info : flash mode : dual-bank

Info : Padding image section 1 at 0x0805aa8c with 4 bytes (bank write end alignment)

Warn : Adding extra erase range, 0x0805aa90 .. 0x0805bfff

Info : wrote 371344 bytes from file main.elf in 1.537886s (235.805 KiB/s)

Info : verified 371340 bytes in 0.903676s (401.291 KiB/s)

Info : Unable to match requested speed 480 kHz, using 200 kHz

Info : Unable to match requested speed 480 kHz, using 200 kHz

shutdown command invoked

> Process Exit Code: 0

> Time Taken: 00:04

ねむいさんが持ってるH5のはrev.Z(0x1001)のはずですが…なんでか

Rev.A(0x1000)になってるんですけぉ…まぁいいかそんあ詳細なこと。

書き込みスピードがメタクソ早くなっているのが救いですね〜

なお、STM32H743のようにバグだらけのRev.Yと修正版のRev.V以降では

まったくの別物になっていたりしたケースがあるのでSTM32H5もこれから

先、Revが上がっていったらとんでもない地雷が待ち受けているかもしれ

ませんがまぁその時はその時で…

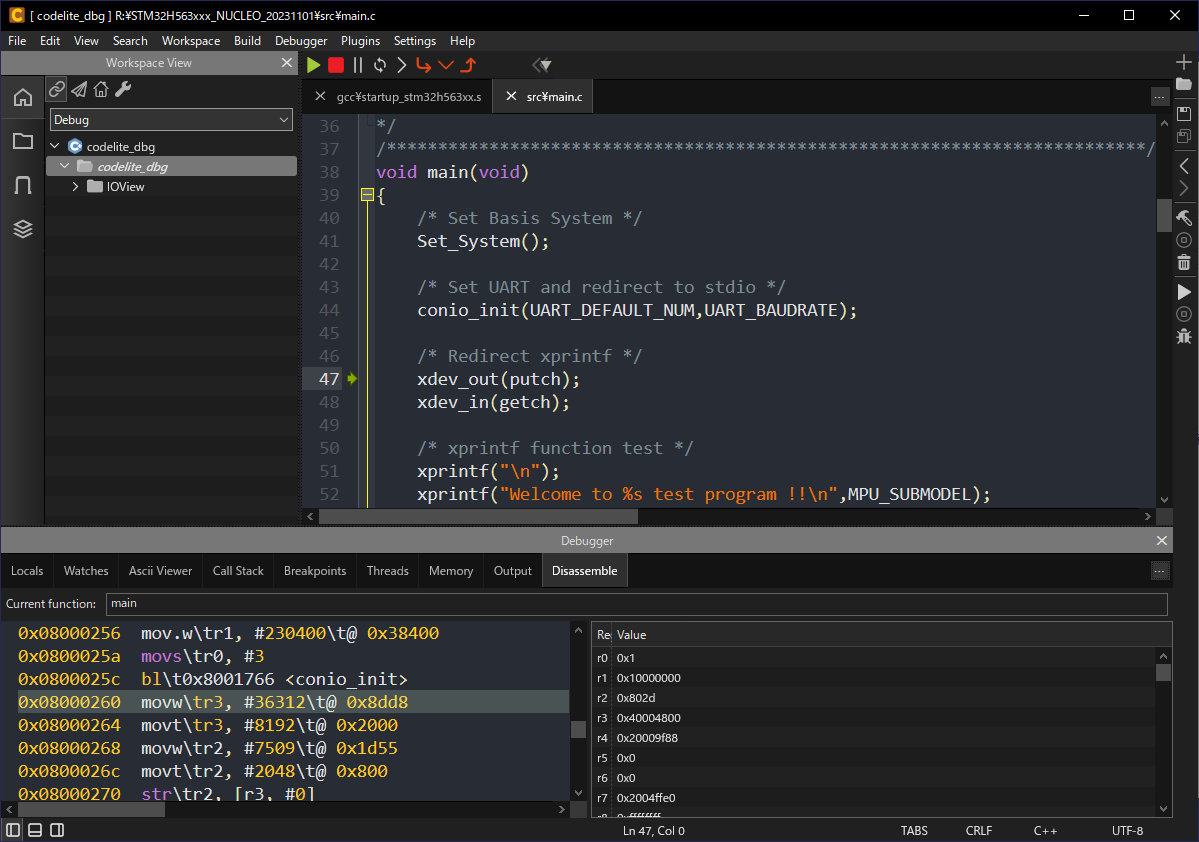

それとTrastZone無し限定ですがデバッグのほうももちろんすいすいと

できちゃいます。H5NucleoならSTLink-V3相当がビルドインされており

キビキビ反応してストレスレスでデバッグが可能です☆

そんなわけで再度紹介になりますが、STM32H5対応OpenOCDバイナリは

私のぶろぐのおきぱで公開しておりますのでH5の基板を持っている方は

どしどしご利用ください!!!

本当はソースコードの基礎部分と、とんでもない罠があるところを解説

したかったのですがOpenOCDだけで力尽きたので次回以降のエントリに

委ねたいと思います…登山ラッシュに入ってますが今年中には足掛かり

くらいは何とか気力振り絞って記事書きたいな〜と思ってます。

H5のプロジェクト自体はすでに公開しておりますので

それまでに皆様予習をお願いいたします…zzz

免責・連絡先は↑のリンクを

↓SNSもやってます↓

powered by まめわざ

powered by まめわざ

- ARM/STM32 (119)

- OpenOCD (27)

- ARM/NxP (34)

- ARM/Cypress (5)

- ARM/Others (3)

- ARM/Raspi (1)

- AVR (13)

- FPGA (4)

- GPS/GNSS (20)

- MISC (87)

- SDCard_Rumors (1)

- STM8 (2)

- Wirelessなアレ (16)

- おきぱ (1)

- ぱそこんの大先生 (2)

- ブラウザベンチマーク (31)

- 日本の自然歩道 (28)

- SDカードとかUSBメモリにSystem Volume Information絶対作らせなくする方法Win11版

⇒ ねむい (01/28) - SDカードとかUSBメモリにSystem Volume Information絶対作らせなくする方法Win11版

⇒ (01/28) - SDカードとかUSBメモリにSystem Volume Information絶対作らせなくする方法Win11版

⇒ (01/28) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ねむい (11/24) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ひかわ (11/24) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ひかわ (11/24) - マイコンでSDカード使うときは必ずプルアップしてね☆

⇒ ひかわ (11/24) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ Kenji Arai (05/29) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ ねむい (05/26) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ Kenji Arai (05/24)

- January 2026 (1)

- December 2025 (4)

- November 2025 (1)

- October 2025 (1)

- September 2025 (1)

- August 2025 (1)

- July 2025 (1)

- June 2025 (1)

- May 2025 (1)

- April 2025 (1)

- March 2025 (1)

- February 2025 (1)

- January 2025 (1)

- December 2024 (2)

- November 2024 (1)

- October 2024 (1)

- September 2024 (1)

- August 2024 (1)

- July 2024 (1)

- June 2024 (1)

- May 2024 (1)

- April 2024 (1)

- March 2024 (1)

- February 2024 (2)

- January 2024 (1)

- December 2023 (4)

- November 2023 (2)

- October 2023 (2)

- September 2023 (1)

- August 2023 (2)

- July 2023 (1)

- June 2023 (2)

- May 2023 (3)

- April 2023 (1)

- March 2023 (1)

- February 2023 (1)

- January 2023 (1)

- December 2022 (2)

- November 2022 (1)

- October 2022 (1)

- September 2022 (1)

- August 2022 (1)

- July 2022 (1)

- June 2022 (1)

- May 2022 (1)

- April 2022 (1)

- March 2022 (1)

- February 2022 (1)

- January 2022 (1)

- December 2021 (2)

- November 2021 (2)

- October 2021 (1)

- September 2021 (1)

- August 2021 (1)

- July 2021 (1)

- June 2021 (1)

- May 2021 (1)

- April 2021 (1)

- March 2021 (1)

- February 2021 (1)

- January 2021 (1)

- December 2020 (3)

- November 2020 (1)

- October 2020 (1)

- September 2020 (1)

- August 2020 (1)

- July 2020 (1)

- June 2020 (2)

- May 2020 (1)

- April 2020 (1)

- March 2020 (1)

- February 2020 (1)

- January 2020 (1)

- December 2019 (3)

- November 2019 (1)

- October 2019 (1)

- September 2019 (2)

- August 2019 (1)

- July 2019 (1)

- June 2019 (1)

- May 2019 (1)

- April 2019 (1)

- March 2019 (1)

- February 2019 (1)

- January 2019 (1)

- December 2018 (3)

- November 2018 (2)

- October 2018 (1)

- September 2018 (1)

- August 2018 (1)

- July 2018 (1)

- June 2018 (1)

- May 2018 (1)

- April 2018 (2)

- March 2018 (1)

- February 2018 (1)

- January 2018 (1)

- December 2017 (2)

- November 2017 (2)

- October 2017 (1)

- September 2017 (1)

- August 2017 (1)

- July 2017 (1)

- June 2017 (1)

- May 2017 (1)

- April 2017 (1)

- March 2017 (2)

- February 2017 (2)

- January 2017 (2)

- December 2016 (7)

- November 2016 (2)

- October 2016 (2)

- September 2016 (1)

- August 2016 (1)

- July 2016 (1)

- June 2016 (1)

- May 2016 (2)

- April 2016 (1)

- March 2016 (2)

- February 2016 (1)

- January 2016 (1)

- December 2015 (3)

- November 2015 (1)

- October 2015 (3)

- September 2015 (2)

- August 2015 (2)

- July 2015 (3)

- June 2015 (3)

- May 2015 (4)

- April 2015 (2)

- March 2015 (4)

- February 2015 (1)

- January 2015 (3)

- December 2014 (3)

- November 2014 (2)

- October 2014 (1)

- September 2014 (2)

- August 2014 (2)

- July 2014 (3)

- June 2014 (2)

- May 2014 (1)

- April 2014 (1)

- March 2014 (4)

- February 2014 (4)

- January 2014 (3)

- December 2013 (5)

- November 2013 (4)

- October 2013 (3)

- September 2013 (2)

- August 2013 (2)

- July 2013 (2)

- June 2013 (3)

- May 2013 (2)

- April 2013 (2)

- March 2013 (2)

- February 2013 (2)

- January 2013 (3)

- December 2012 (4)

- November 2012 (2)

- October 2012 (2)

- September 2012 (4)

- August 2012 (1)

- July 2012 (3)

- June 2012 (2)

- May 2012 (3)

- April 2012 (3)

- March 2012 (2)

- February 2012 (3)

- January 2012 (3)

- December 2011 (5)

- November 2011 (3)

- October 2011 (2)

- September 2011 (2)

- August 2011 (2)

- July 2011 (2)

- June 2011 (2)

- May 2011 (2)

- April 2011 (2)

- March 2011 (2)

- February 2011 (2)

- January 2011 (3)

- December 2010 (7)

- November 2010 (1)

- October 2010 (1)

- September 2010 (1)

- August 2010 (3)

- July 2010 (4)

- May 2010 (1)

- April 2010 (2)

- March 2010 (2)

- February 2010 (2)

- January 2010 (3)

- December 2009 (3)

- November 2009 (8)

- October 2009 (7)

- September 2009 (5)

- August 2009 (4)

- July 2009 (6)

- June 2009 (6)

- May 2009 (14)

- January 1970 (1)

Copyright(C) B-Blog project All rights reserved.

Comments

Post a Comment