STM32F7を使ってみる5 -AXIMとITCM-

STM32F7の内蔵フラッシュメモリは以下に示す2系統のインターフェースで命令

コードを読み出し実行することが可能です。

The AXI-Master (AXIM) interface

TCM Interface

Embedded Workbenchマニアのページさんの記事を参考にして私なりに両者の

性能の違いを確かめてみました。また、各モードで上手く使いこなすための

コツも紹介します。

●AXIM経由のフラッシュ

こちらはCubeF7の各種サンプルプログラムでデフォルトで使用されているスタン

ダードなものです。フラッシュメモリのアドレスは0x08000000に配置されており

過去のSTM32シリーズと同様の感覚で使用できます。

フェッチされた命令はCortex-M7コア内のI-Cacheを有効にしていればフラッシュ

のアクセス速度の遅さを補うことができますのでフラッシュの素のアクセス速度

の遅さを気にせず過去のSTM32シリーズとほぼ同様に使用することができます。

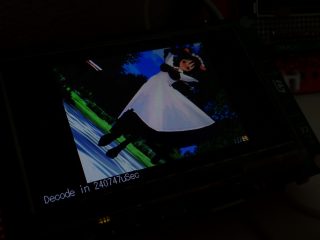

そんなわけで早速表示です。SDRAMのタイミングを正しい値に修正したこと以外は

前回お見せした対策その1と同じ構成です。

●ITCM経由のフラッシュ

ITCMバスにはF2/F4シリーズでおなじみのARTアクセラレータが乗っかっています。

I-Cacheは経由しませんがアクセラレータのおかげでフラッシュの素の(ry

ちなみにITCM経由のフラッシュアクセスの場合、アドレスは0x00200000に配置され

ている事になります。ITCM経由で動かしたい場合はリンカスクリプトの開始アドレスを

0x00200000にしましょう。

なんとこちらの方が高速です!Embedded Workbenchマニアのページさんでも述べられ

ているとおりAXIM経由の場合はフラッシュの命令の他に様々なペリフェラルが行き

かっているので命令はITCMに押しやるのが本来取るべきスジなのでしょう。

●ITCMるコツ

上記の結果だけ見るとAXIMのメリットないじゃんてお思いの方が多いと思います。

残念ながらITCMも結構ピーキーな性質でスムーズに開発を行うために知っておかな

ければならないいくつかのコツがあります。

1.ITCMのアドレスではDMA出来ない

RMを読む限りではバスがDMAコントローラのどこにもつながってないのでこの

アドレスではDMAが一切出来ないと思います。DMA元にconstを決め打ちする

ような転送ではHardFaultになって失敗するでしょう。

もちろんITCMバスにぶら下がっているITCM-RAMもDMA不可能です。

このへんF4のCCMと同じ位置づけですね。

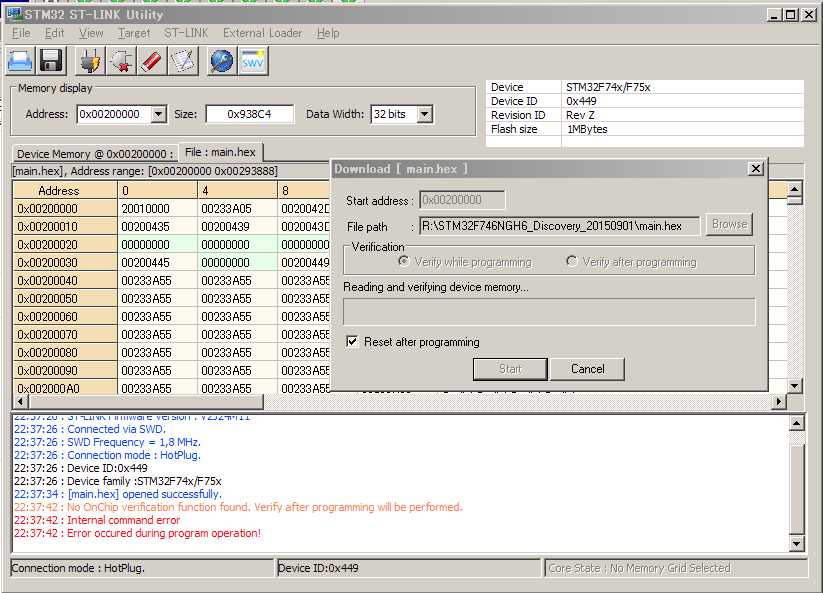

2.フラッシュは0x08000000に焼く

ITCMから見えるフラッシュのアドレスは0x00200000ですがそのアドレスには

フラッシュメモリの実体はなく、過去のSTM32シリーズと同じ0x08000000に

あります。0x00200000に無理やり書こうとしても弾かれます。

↑こんな風にエラー出て駄目です。

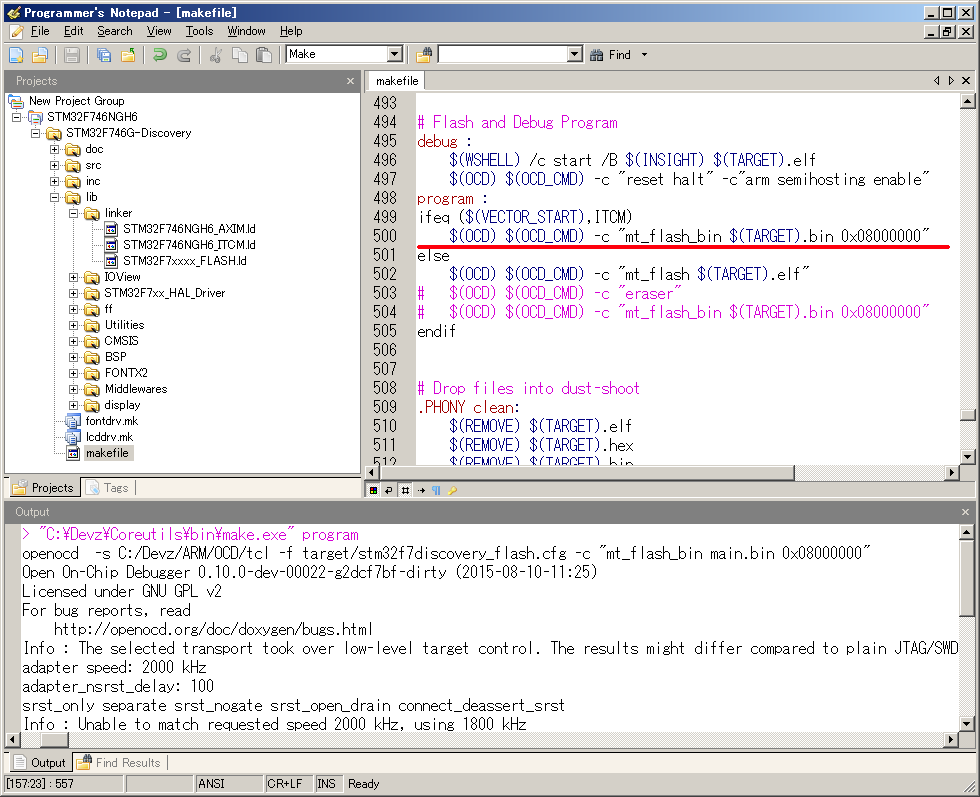

したがってOpenOCDではhexやelf形式のフラッシュ書き込みは100%失敗しますので

binファイルを0x08000000に向かって書き込むようにしましょう。

makefile上ではこんな感じです。9/Sにリリースする新版のいつものではフラッシュに

ITCMを選択すると必ずbin形式で書き込むようにmakefileをいじって置きますので

ねむいさんと同じ開発スタイルの人は特に気にせず快適に書き込み&デバッグが

できると思います★

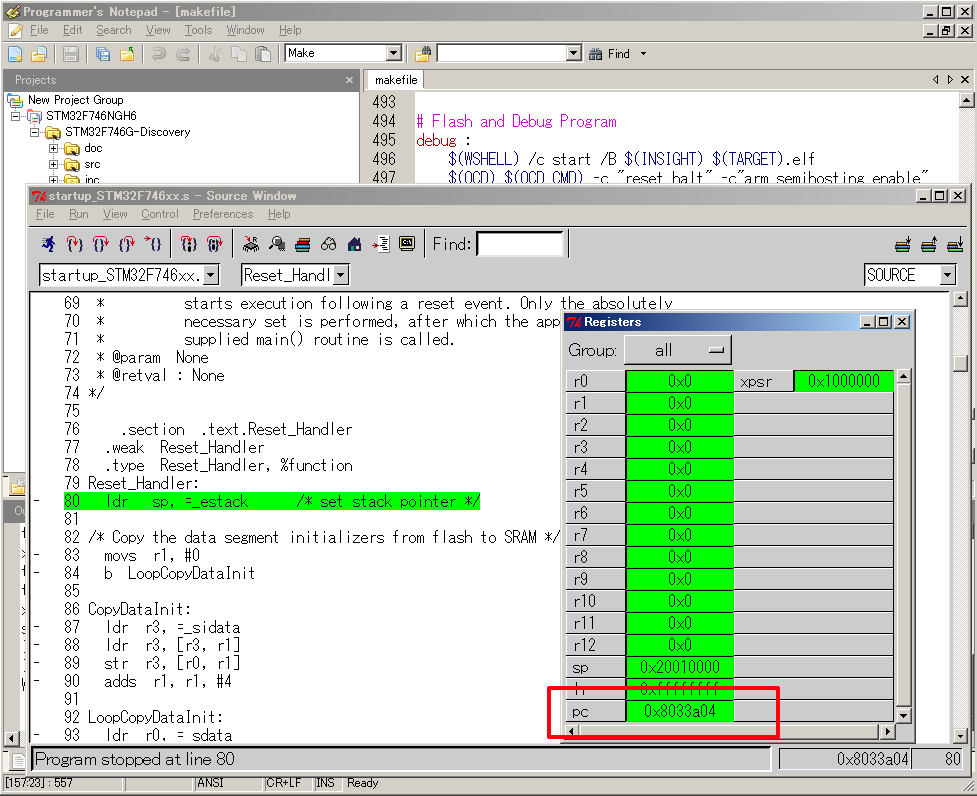

おまけです。

↑AXIMで動かしてる時のデバッグ画面。

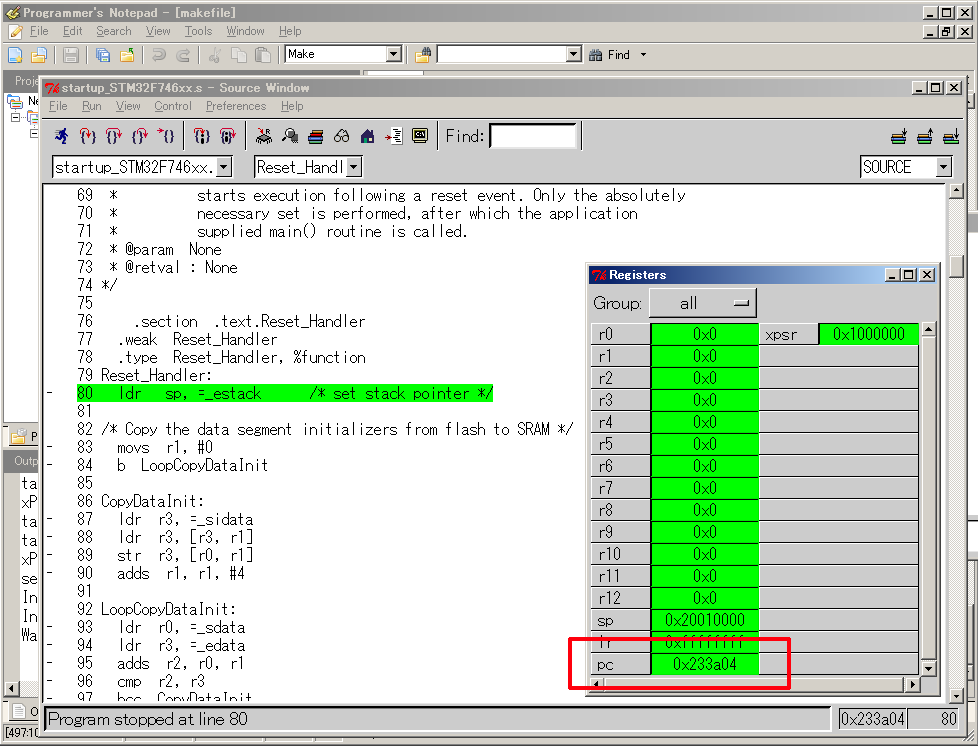

↑ITCMで動かしているときのデバッグ画面。PCの値に注目。

F7シリーズはBOOT0の状態で起動できるアドレスの番地が可変になりましたが、

デフォルトではフラッシュメモリからブートする場合、ITCMインターフェースの先頭

0x00200000から開始になっています。AXIMでもきちんとスタートアップを記述

していれば0x08000000の番地にすぐに飛んでくれるので問題ありません。

・・・徐々に、そして確実にSTM32F7の真の力が明らかになってきています。

今までの私の使ってきたワンチップマイコンの概念のままでは到底その力を引き出す

ことはできないでしょう。しかし私はそれに臆さずどんどん新しい概念に切り込んで

いきたいと思います!!

免責・連絡先は↑のリンクを

↓SNSもやってます↓

powered by まめわざ

powered by まめわざ

- ARM/STM32 (117)

- OpenOCD (27)

- ARM/NxP (34)

- ARM/Cypress (5)

- ARM/Others (3)

- ARM/Raspi (1)

- AVR (13)

- FPGA (4)

- GPS/GNSS (20)

- MISC (85)

- STM8 (2)

- Wirelessなアレ (16)

- おきぱ (1)

- ブラウザベンチマーク (29)

- 日本の自然歩道 (27)

- GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ Kenji Arai (05/29) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ ねむい (05/26) - GNSSモジュールを試用する21 -SAM-M10Qが壊れた…!?と思ったら直せた(おまけあり)-

⇒ Kenji Arai (05/24) - 中部北陸自然歩道を往く -砺波平野の県境を駆け抜ける!-

⇒ ねむい (12/18) - 中部北陸自然歩道を往く -砺波平野の県境を駆け抜ける!-

⇒ ひかわ (12/15) - STM32U0はぢめました

⇒ ねむい (08/07) - STM32U0はぢめました

⇒ ひかわ (07/28) - STM32H5を使ってみる3 -待ち受ける初見殺しの罠たち-

⇒ ねむい (05/17) - STM32H5を使ってみる3 -待ち受ける初見殺しの罠たち-

⇒ どじょりん (05/16) - STM32H5を使ってみる3 -待ち受ける初見殺しの罠たち-

⇒ どじょりん (05/16)

- June 2025 (1)

- May 2025 (1)

- April 2025 (1)

- March 2025 (1)

- February 2025 (1)

- January 2025 (1)

- December 2024 (2)

- November 2024 (1)

- October 2024 (1)

- September 2024 (1)

- August 2024 (1)

- July 2024 (1)

- June 2024 (1)

- May 2024 (1)

- April 2024 (1)

- March 2024 (1)

- February 2024 (2)

- January 2024 (1)

- December 2023 (4)

- November 2023 (2)

- October 2023 (2)

- September 2023 (1)

- August 2023 (2)

- July 2023 (1)

- June 2023 (2)

- May 2023 (3)

- April 2023 (1)

- March 2023 (1)

- February 2023 (1)

- January 2023 (1)

- December 2022 (2)

- November 2022 (1)

- October 2022 (1)

- September 2022 (1)

- August 2022 (1)

- July 2022 (1)

- June 2022 (1)

- May 2022 (1)

- April 2022 (1)

- March 2022 (1)

- February 2022 (1)

- January 2022 (1)

- December 2021 (2)

- November 2021 (2)

- October 2021 (1)

- September 2021 (1)

- August 2021 (1)

- July 2021 (1)

- June 2021 (1)

- May 2021 (1)

- April 2021 (1)

- March 2021 (1)

- February 2021 (1)

- January 2021 (1)

- December 2020 (3)

- November 2020 (1)

- October 2020 (1)

- September 2020 (1)

- August 2020 (1)

- July 2020 (1)

- June 2020 (2)

- May 2020 (1)

- April 2020 (1)

- March 2020 (1)

- February 2020 (1)

- January 2020 (1)

- December 2019 (3)

- November 2019 (1)

- October 2019 (1)

- September 2019 (2)

- August 2019 (1)

- July 2019 (1)

- June 2019 (1)

- May 2019 (1)

- April 2019 (1)

- March 2019 (1)

- February 2019 (1)

- January 2019 (1)

- December 2018 (3)

- November 2018 (2)

- October 2018 (1)

- September 2018 (1)

- August 2018 (1)

- July 2018 (1)

- June 2018 (1)

- May 2018 (1)

- April 2018 (2)

- March 2018 (1)

- February 2018 (1)

- January 2018 (1)

- December 2017 (2)

- November 2017 (2)

- October 2017 (1)

- September 2017 (1)

- August 2017 (1)

- July 2017 (1)

- June 2017 (1)

- May 2017 (1)

- April 2017 (1)

- March 2017 (2)

- February 2017 (2)

- January 2017 (2)

- December 2016 (7)

- November 2016 (2)

- October 2016 (2)

- September 2016 (1)

- August 2016 (1)

- July 2016 (1)

- June 2016 (1)

- May 2016 (2)

- April 2016 (1)

- March 2016 (2)

- February 2016 (1)

- January 2016 (1)

- December 2015 (3)

- November 2015 (1)

- October 2015 (3)

- September 2015 (2)

- August 2015 (2)

- July 2015 (3)

- June 2015 (3)

- May 2015 (4)

- April 2015 (2)

- March 2015 (4)

- February 2015 (1)

- January 2015 (3)

- December 2014 (3)

- November 2014 (2)

- October 2014 (1)

- September 2014 (2)

- August 2014 (2)

- July 2014 (3)

- June 2014 (2)

- May 2014 (1)

- April 2014 (1)

- March 2014 (4)

- February 2014 (4)

- January 2014 (3)

- December 2013 (5)

- November 2013 (4)

- October 2013 (3)

- September 2013 (2)

- August 2013 (2)

- July 2013 (2)

- June 2013 (3)

- May 2013 (2)

- April 2013 (2)

- March 2013 (2)

- February 2013 (2)

- January 2013 (3)

- December 2012 (4)

- November 2012 (2)

- October 2012 (2)

- September 2012 (4)

- August 2012 (1)

- July 2012 (3)

- June 2012 (2)

- May 2012 (3)

- April 2012 (3)

- March 2012 (2)

- February 2012 (3)

- January 2012 (3)

- December 2011 (5)

- November 2011 (3)

- October 2011 (2)

- September 2011 (2)

- August 2011 (2)

- July 2011 (2)

- June 2011 (2)

- May 2011 (2)

- April 2011 (2)

- March 2011 (2)

- February 2011 (2)

- January 2011 (3)

- December 2010 (7)

- November 2010 (1)

- October 2010 (1)

- September 2010 (1)

- August 2010 (3)

- July 2010 (4)

- May 2010 (1)

- April 2010 (2)

- March 2010 (2)

- February 2010 (2)

- January 2010 (3)

- December 2009 (3)

- November 2009 (8)

- October 2009 (7)

- September 2009 (5)

- August 2009 (4)

- July 2009 (6)

- June 2009 (6)

- May 2009 (14)

- January 1970 (1)

Copyright(C) B-Blog project All rights reserved.

Comments

はじめまして。

興味深く拝見しております。

当方、AtmelのCoretex-M7 SAMS70をミュージックシンセに組み上げようとしております。

以下、不躾な質問で申し訳ありません。

キャッシュのことなのですが、

CMSISにSCB_CleanInvalidateDCache_by_Addrという関数がありますが、KeilのHPにあります。

これは特定の領域をキャッシュ無効にできるというものなのでしょうか?

シンセサイザーの場合、CPUは、波形データを吐きだす(書き込む)ばかりですので、

キャッシュ無効でもいいのか?あるいは、もっといい方法があるのか探ってみたいです。

DMAはSRAMに書かれた512ロングワードのデータを44.1KHzのサンプリング周期でI2Sに転送していきます。

バッファはピンポンバッファになっていて、11.6mS周期のDMA転送のたびに切り替えるようにします。

コンパイラーはKeil MDK μVisionFree版です。

p.igmon様はじめまして、ねむいです。

ATMEL系はAVRとXMEGAしか全く知らないのですがコアとしては

一緒のはずなので分かる範囲でお答えします。

SCB_CleanInvalidateDCache_by_AddrはD-Cacheの一ライン

(Cortex-M7では32バイト単位)ごとにinvalidateしてcleanする

関数です。invalidateはキャッシュそのものを無効化するのでは

なく"内容"を無効化します。

DMAする際にはちゃんとメモリのサイズやアライメントを考慮

していないとこれを行っていても関係ない領域まで破壊される

ので細心の注意を払ってください。

一方で速度の低下を受け入れてD-Cacheそのものを特定のメモリ

領域で無効化したい場合はMPUから無効にする領域を設定します。

ただし設定できるメモリ領域の範囲はそれほど細かく指定できない

のである程度妥協が必要です。

私としましてはキャッシュの影響を受けないDTCMをDMA用に確保する

ことを考えます。特にATMEL系はDTCMのサイズをユーザーレベルで

変えられますのでつぶしが利くはずです。

TCMに転送バッファを置くのが良さそうなこと、ご指摘ありがとうございます。

CPUが届くのはまだ先のようですが、Atmelのほうですが、TCMメモリのサンプルプログラムがあり、

これらをコンパイルして、メモリMAPを確認してみます。

Post a Comment